- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

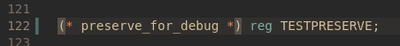

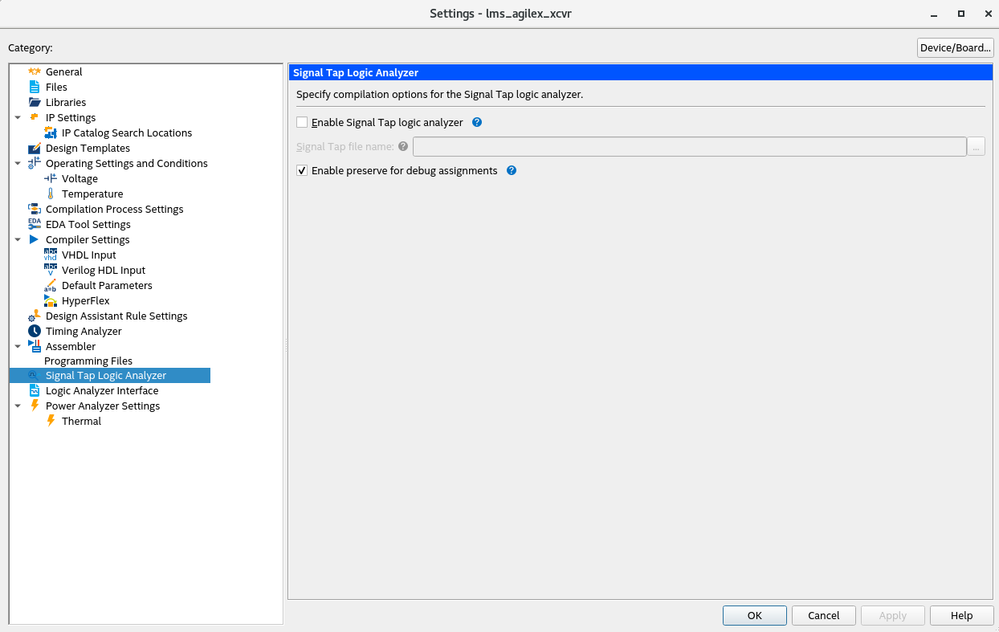

1. I follow the steps "2.4.1. Preserving Signals for Monitoring and Debugging" in 683819

2. I watched and followed this Intel-FPGA video: https://www.youtube.com/watch?v=sEKc2ut42gU

What do I do wrong?

Quartus Pro 22.1

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Alright thanks for the feedback. I've let them know that you expect this fix to apply to all data types.

In the meantime your only workaround is to have the signal connected to an i/o port.

With that, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

Regards,

Nurina

P/S: If you like my comment, feel free to give Kudos. If my comment solved your problem, feel free to accept my comment as solution.

Link Copied

- « Previous

-

- 1

- 2

- Next »

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Nurina,

Please define "use". The signal exists, it's driven by something but doesn't have any fanouts. (it can be a link_up, some counters or anything meaningful only for debugging purpose)

Also, as @sstrell suggested, adding the signal as virtual pin doesn't change anything, the signal is still optimized out.

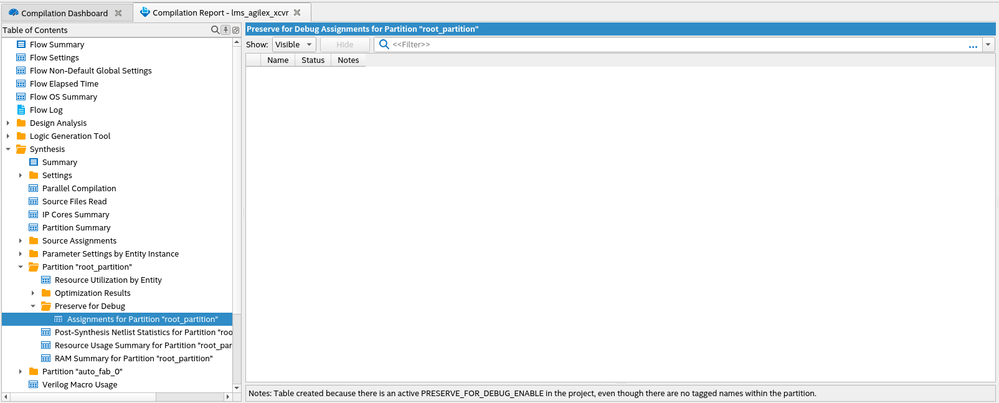

After Analysis&Synthesis:

This needs to be fixed.

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I've also tried via the Assignment Editor:

set_instance_assignment -name PRESERVE_FOR_DEBUG ON -to *sigtodebug*without success. The signal isn't kept.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

By use, I meant that it's driven by something with fanouts. Although with this attribute we should expect it to be preserved no matter what.

This looks like a bug, I'm reporting this issue to our engineering team. I will let you know of any updates.

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for the confirmation @Nurina.

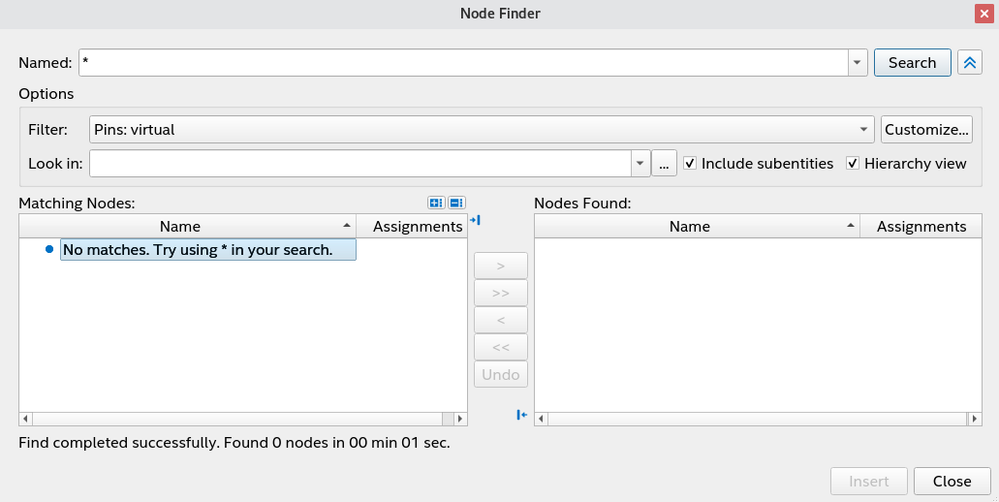

I've been trying to use this attribute for few days now, it has never worked properly.

Some times I can see the signal under "Preserved for debugging" in the "Node Finder" but the signals are driven and have fanouts, nevertheless even without the attribute they wouldn't be optimized away and are present under "Pre-synthesis".

My question was about a very simple case to show the bug, my use case is mostly using typedef and struct (packed).

typedef struct {

logic init;

logic [3:0] b;

} t_data;

(*preserve_for_debug*)t_data tx;

(*preserve_for_debug*)t_data rx;

(*preserve_for_debug*)t_data tx_array[4];

(*preserve_for_debug*)t_data rx_array[4];

Please make sure this is also possible using any data types of Verilog/SystemVerilog.

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

This problem has been previously reported to the engineering team and they are currently working on a fix for a future version of Quartus. I'm checking with them if there is a workaround you can use while waiting for the permanent fix.

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you, will it be in a future version (few months) or a patch (few days)? What's the time frame we can expect it to be working?

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The fix is for a future version, so it will take a few months.

For now, a workaround would be to connect the signal to a top-level output port.

Could you attach your design? The engineering team might be able to do something to help with your situation.

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you.

I can't attach my design, the basic use cases don't work.

They can find some examples in my previous messages above. (+enum +mixed packed/unpacked arrays +...)

Looking forward to being able to use this feature.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Alright thanks for the feedback. I've let them know that you expect this fix to apply to all data types.

In the meantime your only workaround is to have the signal connected to an i/o port.

With that, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

Regards,

Nurina

P/S: If you like my comment, feel free to give Kudos. If my comment solved your problem, feel free to accept my comment as solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Quartus pro 23.1, we still have issues with preserve_for_debug...

This will never ends...

IPS case opened, I just comment here for tracking purpose.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »