- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hey all,

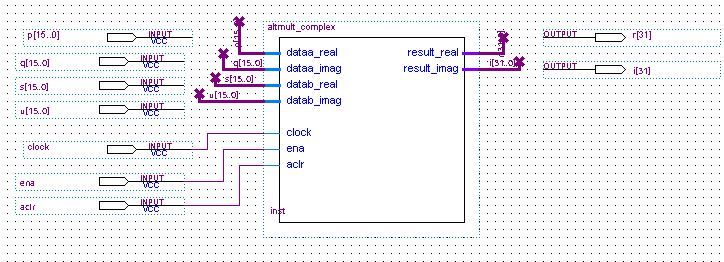

I'm trying to implement ALTMULT_COMPLEX for complex numbers, However, when I came to implement the circuit, it shows that all input sizes are mismatch. Can you please help with that? an image is attached.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It's really hard to see in your picture what the signal name is on dataa_real, but it looks like it should be p[15..0] to match the input you have. Can you post the error message(s) you're getting?

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

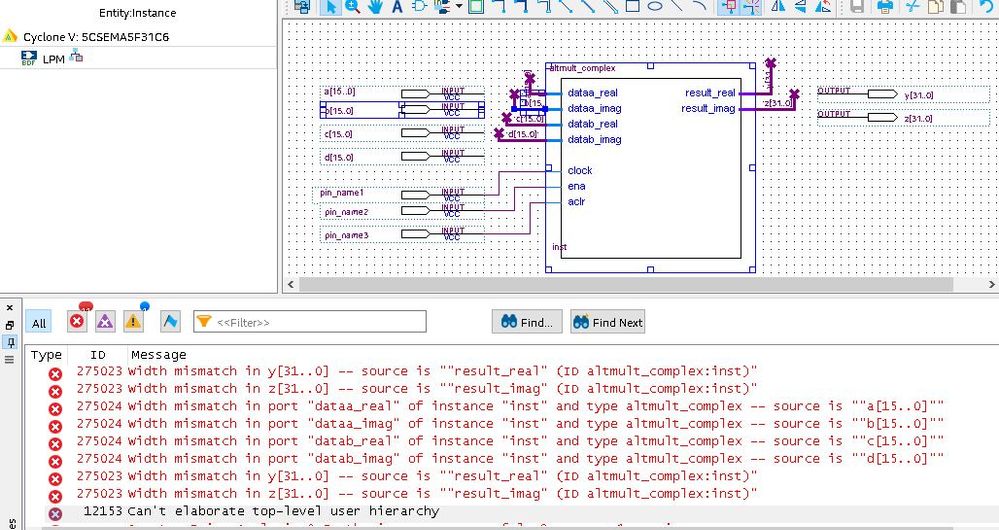

Thanks for your reply, i'm trying to implement altmult_complex circuit with two inputs (each has 32 bits) and one output with 64 bits.

the names are identical with the inputs. here is the error message.

would be very grateful if you could help me.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Oh, if you're going to not directly connect the I/O to the bus wires of altmult_complex, you need to add bus wires to the I/O and name them appropriately. The tool thinks your I/O are all single bit. I/O naming in the schematic editor is separate from internal signal naming. Your I/O objects are right next to the block. Why not just connect them directly?

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

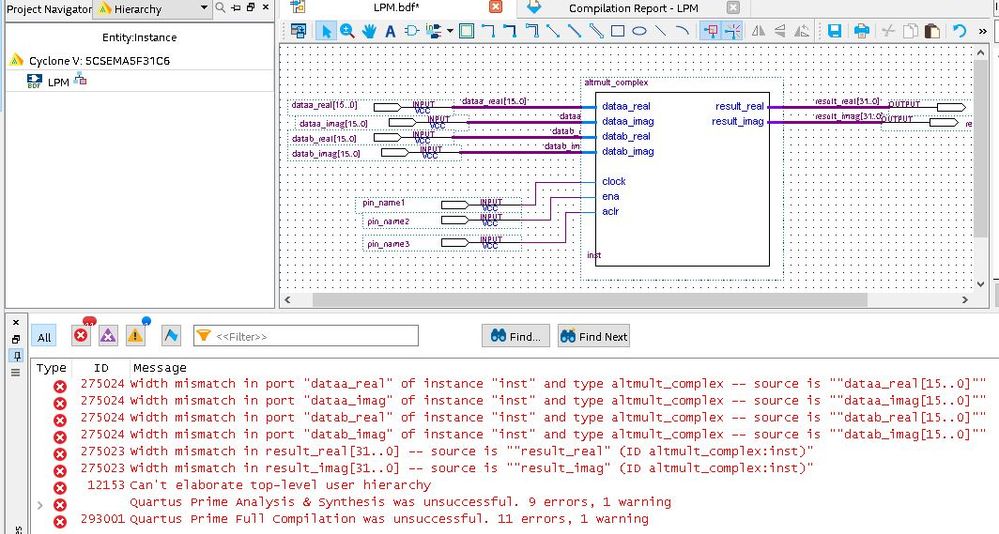

I did, i connected them directly but got the same message again.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Weird. Can you post the updated schematic?

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Well, if it's not the pins or signals, then it must be your settings for the IP. Double-click it and make sure the widths are set correctly.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Just wonder if you have had a chance to try the following:

- In your schematic, delete all the wires, pins and the altmult_complex instance

- Launch the Megawizard for the altmult_complex IP in your design and regenerate the HDL and BSF

- Add the new BSF into schematic

- Right-click on the instance -> Generate Pins. This should auto-generate the input/output pins with the corresponding width

- Run the compilation again to see if issue still persist

If issue still persist, please help to attach your test design QAR so that I can further look into it. Thank you very much.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page