- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We are working on Quartus Version : Quartus Prime Version 21.1.0 Build 169 03/24/2021 SC Pro Edition

Target Device: 1SG280HU2F50E2VG

Added "External Memory Interfaces Intel Stratix 10 FPGA IP" on Quartus Platform Designer.

Enabled preset filter: Stratix 10 GX H-Tile FPGA Development Kit with DDR4 HILO

Changed Memory -> Topology-> DQ width from 72 to 32 to change Avalon interface Data width to 256bits. This change has popped up below two Errors

Cannot place ALERT# in DQS group 8 since the group value is out of range

"DQS group of ALERT#" (MEM_DDR4_ALERT_N_DQS_GROUP) 8 is out of range: 0,1,2,3

Changed "ALERT# pin placement" from "I/O lane with DQSGroup" to "Automatically select a location"

Are these valid changes?

I still see below warning

Warning: emif_s10_0: The selected board is 'Stratix 10 GX H-Tile FPGA Development Kit with DDR4 HILO'. Ensure that a development kit preset is applied before generating the example design; do not modify the IP parameters. For verified development kit test results, the selected development kit preset text should be bolded in the Presets panel.

What is the action for this Warning?

Regards

Siva Kona

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

When you created the Quartus project, did you select that board in the New Project Wizard?

You made changes from the preset, so it's warning you that you made changes from that preset so the design may not work with the board you selected. If you're OK with this, you can ignore the warning.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sstrell, Thanks for your reply.

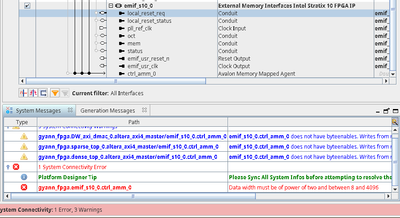

Preset configuration of "Stratix 10 GX H-Tile FPGA Development Kit with DDR4 HILO" shows following Errors

emif_s10_0.ctrl_amm_0 Data width must be of power of two and between 8 and 4096

This is because the DQ width value 72 sets the Avalon MM Interface Data width as 576.

We have changed the DQ width from 72 to 32, to align the ctrl_amm_0 data width(256 bits) to the other modules in the system

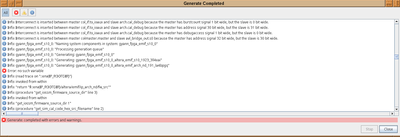

This change resulted in following Errors during Generate HDL run.

Error: no such variable

Error: Generation stopped, 2 or more modules remaining

Error: qsys-generate failed with exit code 1: 2 Errors, 1 Warning

Error: SPD file was not generated: /nfs/site/disks/hpg_meu/snkona/22WW06_GyANN_FPGA/ip-gyann-fpga/s10gx/fpga_gdlj_onchipmem/qips/ip/gyann_fpga/gyann_fpga_emif_s10_0/gyann_fpga_emif_s10_0.spd

Error: Could not generate simulation scripts

Error: no such variable

Error: Generation stopped, 2 or more modules remaining

Error: qsys-generate failed with exit code 1: 2 Errors, 1 Warning

Regards

Siva Kona

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As noted, did you synch the system infos after you made the parameter change? Just click Sync System Infos at the bottom of Platform Designer.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sstrell,

"Sync System infos" also did not change the behavior. Got same Errors as before.

Following is the snapshot of the messages around first Error

Regards

Siva Kona

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Don't even bother trying to generate if you have any red error messages. It will always fail.

If you're still seeing the power of 2 error, check whatever is connected on the other side. Something is mismatched or incorrect. It could be as simple as removing a connection and then adding the connection back in to refresh the system.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Siva Kona,

Changed "ALERT# pin placement" from "I/O lane with DQSGroup" to "Automatically select a location"

Are these valid changes?

- Yes the change is valid.

Do you see any error message in the qsys?

What is the DQ pins per DQS group that you used?

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Adzim,

DQ pins per DQS group is 8

My Intel employee ID is 11594082. Could you please ping me to take a quick look at the the tool?

Regards

Siva Kona

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Siva,

I have sent an email to you regarding to your request.

Please let me know if you not receive the email.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Update: Using the workaround from the KDB in the link below has solved the issue.

https://www.intel.com/content/www/us/en/support/programmable/articles/000087056.html

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page