- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

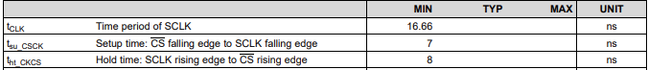

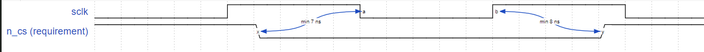

I am currently working on a ADC driver interface and I have come across the following timing requirement for the chip-select signal. My sclk is running at 50MHz, 20ns time period. Notice that both sclk and n_cs is driven by the FPGA, while the requirements are seen from the ADC.

As we can see, there is one requirement for rising edge of n_cs and another for the falling edge.

In my current implemented solution, the n_cs signal is

- set low on sclk rising edge

- set high on sclk falling edge

This functionality is implemented using a combination of two processes, one for rising_edge(sclk), while a delayed signal is created using falling_edge(sclk). (VHDL)

The sclk is also used as output to the ADC, and is properly constrained as a 50MHz clock internally and as a generated (virtual) clock on the FPGA output pin.

My problem is that I do not understand how n_cs should be constrained on the FPGA output.

Using the chosen topology, would it be enough for the n_cs signal to have the same propagtaion delay to the FPGA pin as sclk (assuming equal PCB trace delay for sclk and n_cs)? In that case, how would I go about setting up such a constraint?

I would appreciate any insight into this problem.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you show the SDC you have so far?

n_cs is just an output so you would use set_output_delay.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sstrell.

The following constraints applies for the driver clock and the n_cs output port:

# First, a 50Mhz clock is made by toggeling the clk_50 register in a 100MHz process. The 50 Mhz clock source is constrained as follows:

# Define 50 MHz clock source, derived from 100MHz clock

create_generated_clock -name CLK_50MHZ -source {*|pll1|clk[2]} -divide_by 2 [get_registers {*clk_50}]

# The 50 MHz clock is used for the driver logic and to drive the CS1_AD_CLK output FPGA pin

# Create virtual clock on SCLK output pin. This virtual clock is the referance point for Signals to and from the ADC.

create_generated_clock -name ADC_SCLK -source [get_registers {*clk_50}] -divide_by 1 [get_ports {CS1_AD_CLK}]

# The following constraint is a placeholder for the proper output constraint..

set_false_path -from * -to [get_ports {CS1_AD_NCS}]

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

First, I'm assuming CS1_AD_NCS is the output port for n_cs. As such, you should not have a false path on it (you do mention that's a placeholder). You should, however, have a false path on the clock output so it is not analyzed as a data output (should only be analyzed as a clock).

Then you need set_output_delay for n_cs to tie your output clock to the n_cs output. This is basically a source synchronous output interface. Assuming you're matching the trace lengths for the clock and n_cs, constraints might look like this:

set_output_delay -max 7 -clock [get_clocks ADC_SCLK] [get_ports CS1_AD_NCS] -clock_fall

set_output_delay -min -8 -clock [get_clocks ADC_SCLK] [get_ports CS1_AD_NCS]

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Erlend,

Any updates?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, and sorry for the missing reply!

I was thrown into another project temporarely and will come back to this problem during the next couple of weeks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Since you need more time on this. I will put to close pending and you may reopen this in future or simply create new case.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page