- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hello,

The EMIF project is created based on the below user guide. Compiling and programming on my board was fine. However, the EMIF Debug Toolkit can't link project to device with the below errors.

The full error log and the archived project are attached. Please help me to solve the problem.

Thanks.

1.9. Debugging the Intel® Cyclone® 10 GX EMIF Design Example

Could not accurately determine connection type for connection emif_c10_0|emif_c10_0|em_jtag_0|jtag_phy_embedded_in_jtag_master|node|sld_virtual_jtag_component|sld_virtual_jtag_impl_inst|jtag_signal_adapter|sld_jtag_endpoint_adapter_impl_inst|sld_agent_ep_inst|ep as the clock of the connection is inactive.

Could not accurately determine connection type for connection emif_c10_0|emif_c10_0|col_if|colmaster|jtag_phy_embedded_in_jtag_master|node|sld_virtual_jtag_component|sld_virtual_jtag_impl_inst|jtag_signal_adapter|sld_jtag_endpoint_adapter_impl_inst|sld_agent_ep_inst|ep as the clock of the connection is inactive.

Could not accurately determine connection type for connection emif_c10_0|emif_c10_0|col_if|colmaster|jtag_phy_embedded_in_jtag_master|node|sld_virtual_jtag_component|sld_virtual_jtag_impl_inst|jtag_signal_adapter|sld_jtag_endpoint_adapter_impl_inst|sld_agent_ep_inst|ep as the clock of the connection is inactive.

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi Jeff,

You do not to worry about Fitter location because the Fitter location is auto generated by Quartus.

The important thing here is the location must be able to pass the Fitter compilation.

After you have filled all location according to schematic, you can recompile the design again.

Regards,

Adzim

링크가 복사됨

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi Jeff,

I may suggest to check on pin assignment of the design.

Try to place all the pins then rerun the compilation.

Then you may program the board again and run the EMIF Debug Toolkit.

Regards,

Adzim

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi Jeff,

Is there any feedback or update in this thread?

Regards,

Adzim

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi Adzim,

Sorry. I'm not good at using Quartus yet. So, I don't know how to go ahead with your suggestions.

Could you let me know the steps more in detail? Thanks.

Regards,

Jeff

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi Jeff,

You can use Pin Planner tool from Quartus to fitting the pin assignment.

There is multiple resources about Pin Planner but you may refer to this link as well:

https://www.intel.com/content/www/us/en/docs/programmable/683562/17-1/pin-planner.html

The pin location for memory device should be able to get from board schematic in IO Bank section.

You can fill up the location tab in Pin Planner with the location stated in the board schematic.

Regards,

Adzim

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi Jeff,

Do you have any update in this issue?

Are you able to use Pin Planner tool to place the pins?

Regards,

Adzim

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi Adzim,

I tried to run "I/O Assignment Analysis" on the pin planner. The warning message is attached.

However, I still don't know how to solve the problem with the pin planner.

Best Regards,

Jeff

Info (20273): Intermediate fitter snapshots will not be committed because ENABLE_INTERMEDIATE_SNAPSHOTS QSF assignment is disabled during compilation.

Info (20274): Successfully committed planned database.

Info (12517): Periphery placement operations ending: elapsed time is 00:00:40

Warning (171167): Found invalid Fitter assignments. See the Ignored Assignments panel in the Fitter Compilation Report for more information.

Info: Quartus Prime Fitter was successful. 0 errors, 5 warnings

Info: Peak virtual memory: 8233 megabytes

Info: Processing ended: Wed May 3 17:38:08 2023

Info: Elapsed time: 00:00:46

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi Jeff,

I believe you have to set the pin name in Location tab according to the your board schematic.

After you have placed all pins, you need to run full compilation again.

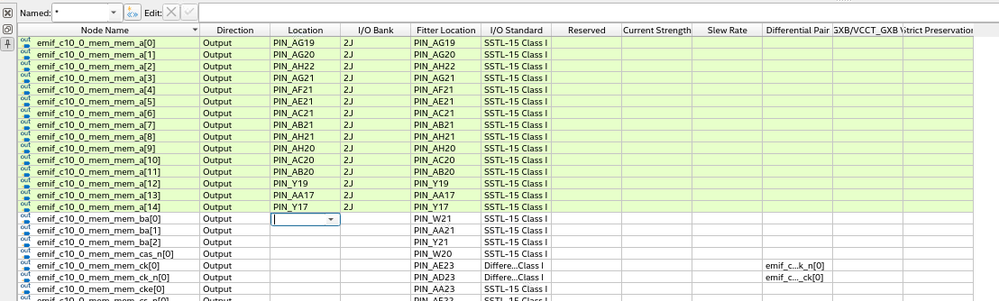

The snapshot below is the example of pin names in the Pin Planner window.

Regards,

Adzim

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi Adzim,

Unfortunately, I haven't filled the location yet. The devboards GmbH designed it but the website stays inactive for long time. So, I can't download its schematics currently.

Best Regards,

Jeff

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi Jeff,

Can you share the link?

I found a link that providing Cyclone 10 GX FPGA module.

Can you check if it's similar to your board?

Regards,

Adzim

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi Adzim,

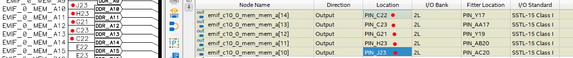

Although the website is inactive, I got the schematic from the employee fortunately. The schematic is the left-hand side of the below screenshot. I filled the location in the pin planner according to the schematic. The location and the fitter location are different unlike your screenshot. Am I doing it correctly?

Best Regards,

Jeff

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi Jeff,

You do not to worry about Fitter location because the Fitter location is auto generated by Quartus.

The important thing here is the location must be able to pass the Fitter compilation.

After you have filled all location according to schematic, you can recompile the design again.

Regards,

Adzim