- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have just moved from Cyclone IV to Cyclone V development.

I also moved to Quartus Prime 22.1std Build 915 SC Lite Edition to Quartus Prime 20.1.0 Build 711 SJ Lite Edition (not sure if 20.1.0 supports the Cyclone V but I upgraded anyway).

I have noticed that it takes a lot longer to compiler and program the Cyclone V device. This is using the same design as used on the Cyclone IV.

Cyclone IV, Quartus Prime 20.1.0 Build 711: 1 minute 7 seconds

Cyclone V, Quartus Prime 22.1std Build 915: 3 minutes 43 seconds

Programming time is now a lot longer too (about 13 seconds):

Info (209060): Started Programmer operation at Mon Dec 12 16:40:08 2022

Info (209016): Configuring device index 1

Info (209017): Device 1 contains JTAG ID code 0x02B220DD

Info (209007): Configuration succeeded -- 1 device(s) configured

Info (209011): Successfully performed operation(s)

Info (209061): Ended Programmer operation at Mon Dec 12 16:40:21 2022

Is there anything I can do (e.g. disable something) so that my compile times are faster?

This is really killing my enthusiasm with my hobby at the moment.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

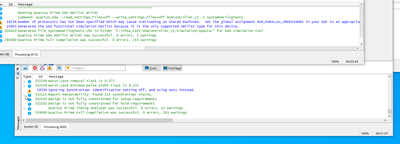

A more complicated larger device is going to require more compile and programming time. You can reduce compile time by adjusting optimization options for the compiler or making sure you are using all the cores of your computer. See the warning message in your screenshot. You can also turn off the running of the EDA netlist writer stage of the compiler unless you need to generate files for a third-party tool.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

A more complicated larger device is going to require more compile and programming time. You can reduce compile time by adjusting optimization options for the compiler or making sure you are using all the cores of your computer. See the warning message in your screenshot. You can also turn off the running of the EDA netlist writer stage of the compiler unless you need to generate files for a third-party tool.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@sstrell I just changed the EDA Tool Settings -> Simulation setting to "None" .. and turned off Advanced Physical Optimization.

The compiler time has dropped to 1:18 !!

Thanks for the additional hint. This will make such a big difference. I can live with the additional programming time but the 4 minute compile time was a big killer.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page