- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

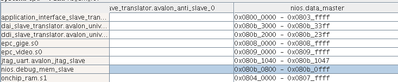

I am having an issue with elaborating generated files from a Platform Designer project. I inherited a CPU project and needed to add interfaces to it so I could connect it to other Avalon bus designs in my project. I intended to add three Avalon MM Slave Translators which are in the picture below as application_interface, dai, and ddi.

However, anytime I add a new module to this project, generate HDL, and try to run Analysis & Synthesis I get the following error messages:

Info (12128): Elaborating entity "cpu_altera_merlin_router_181_wpeblfi" for hierarchy "gvrd:gvrd_0|cpu:CPU_INST|cpu_altera_mm_interconnect_181_nbk4cfi:mm_interconnect_0|cpu_altera_merlin_router_181_wpeblfi:router" File: /home/jdoher ty/ddm/exe_rh_icb_fw/hdl/lib_euresys_ip/gvrd-a10gx-tpg-fb_fifo/cpu/cpu/altera_mm_interconnect_181/synth/cpu_altera_mm_interconnect_181_nbk4cfi.v Line: 2552

Error (10232): Verilog HDL error at cpu_altera_merlin_router_181_wpeblfi.sv(208): index 32 cannot fall outside the declared range [31:0] for vector "address" File: /home/jdoherty/ddm/exe_rh_icb_fw/hdl/lib_euresys_ip/gvrd-a10gx-tpg-f b_fifo/cpu/cpu/altera_merlin_router_181/synth/cpu_altera_merlin_router_181_wpeblfi.sv Line: 208

Error (12152): Can't elaborate user hierarchy "gvrd:gvrd_0|cpu:CPU_INST|cpu_altera_mm_interconnect_181_nbk4cfi:mm_interconnect_0|cpu_altera_merlin_router_181_wpeblfi:router" File: /home/jdoherty/ddm/exe_rh_icb_fw/hdl/lib_euresys_ip/ gvrd-a10gx-tpg-fb_fifo/cpu/cpu/altera_mm_interconnect_181/synth/cpu_altera_mm_interconnect_181_nbk4cfi.v Line: 2552

If I remove the added interfaces and rebuild it once again passes elaboration.

I am using Quartus Prime Version 18.1.0 Build 625 09/12/2018 SJ Standard Edition which is a requirement for my project.

Has anyone seen this error before and is there any way to work around it?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you try an experiment and add an Avalon to External bus Bridge and then connect a slave to that to see if that compiles?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Joseph,

I found a KDB related to your issue, might have to see it

Thanks,

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I've tried moving one of the slaves up to 0x7800_0000-0x7803_ffff but that didn't seem to work. I also grouped all of the new slave interfaces into one and gave that a larger address width which also didn't work.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you try an experiment and add an Avalon to External bus Bridge and then connect a slave to that to see if that compiles?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you, that did compile.

Any idea why there is a difference between the External bus Bridge and the Slave Translator?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page