- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, I had trouble compiling a simple module :

Error (293007): Current module quartus_map ended unexpectedly. Verify that you have sufficient memory available to compile your design. You can view disk space and physical RAM requirements on the System and Software Requirements page of the Intel FPGA website (http://dl.altera.com/requirements/).

I simplified my code to look like this:

module convlayerSingle(inputPart,addr,outputWhole);

input [0:16-1] inputPart;

input [9:0] addr;

output reg [0:1024*16-1] outputWhole; //32*32*16

always @ (*) begin

//outputWhole = 0;

outputWhole[addr*16+:16] = inputPart[0:16-1];

end

endmodule

My experiment showed that the error occurred because the bit width of outputWhole was too large, but it was only 25*25*16, which was a very small picture.

And I tested the same code on vivado with no errors. Is my code style inappropriate? Or should I do something special with Quartus?

(There are 16 GB of memory in the my computer, and quartus takes up 12 GB when compiling, so I don't think it's likely to be a software version or computer configuration problem.)

Can any one help me please?

Thank you in advance.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What does the + do here:

outputWhole[addr*16+:16]

And because of your endianness, doesn't "addr*16+" have to always be between 0 and 15 (<16 that is)?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your reply!

In fact, "+:" and "- :" are syntax in verilog2001.

"That syntax is called an indexed part-select. The first term is the bit offset and the second term is the width. It allows you to specify a variable for the offset, but the width must be constant."

I tried to change my code to show you what this syntax does, like this:

module convlayerSingle(inputPart,addr,outputWhole);

input [0:16-1] inputPart;

input [9:0] addr;

output reg [0:1024*16-1] outputWhole; //32*32*16

integer i;

always @ (*) begin

//outputWhole = 0;

//outputWhole[addr*16 +: 16] = inputPart[0:16-1];

for(i=0;i<16;i=i+1) begin

outputWhole[addr*16+i]=inputPart[i];

end

end

endmoduleBut something unexpected happened: Quartus finished compiling the changed code in a very short time, and there were no errors!

Well, maybe Quartus doesn't support this weird syntax?

Thanks again for your reply, it was you who helped me solve this problem!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Quartus tool does support +: and -: part-selects.

Reference:

Instead, I saw these errors when try to run fitter stage. You may need to check your design.

Error(22412): The design requires at least 16419 elements of type IO_CLUSTER but the device has only 1857.

Error(22412): The design requires at least 16393 elements of type IO_OUTPUT_BUFFER but the device has only 1037.

Error(22412): The design requires at least 16419 elements of type IO_PAD but the device has only 1269.

Error(16297): An error has occurred while trying to initialize the plan stage.

Best Regards,

Richard Tan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your attention to my question!

I used virtual pins to avoid the errors you pointed out.

But it still doesn't explain why code with "+ : "compiles out of memory, while code with the same functionality compiles quickly with no errors.

Sometimes it is unavoidable to use "+ :" and "- :" for dynamic interception of fixed bit width. That's when I hit a standstill...So should I set up Quartus to support "+ :"?

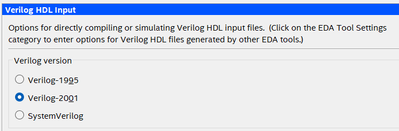

In fact, I have selected the Verilog version as Verilog-2001:

I would be grateful if you could give me your advice!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Now that I check closely, I believe there is some weird behavior happening behind the compilation. (could be a bug)

I saw the Error (293007) occur with Quartus Standard 22.1 if using insufficient memory. When allocated a larger memory, it took me ~16m47s to finish the Analysis & Synthesis (using the +: indexed part-select) as compared to ~1m30s using other design. (without +: )

If I use Quartus Pro 22.4, both designs compiled successfully in 25 seconds. So something must have gone wrong with standard version.

I will file a case to the engineering team to investigate on this.

Best Regards,

Richard Tan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Unfortunately, the engineering team only do maintenance for Quartus standard so this issue is most likely not gonna be fixed as there is a workaround available (using a machine with more memory, changing code or use Quartus Pro version). I am sorry that I can't help you much on this,

Let me know if you need further help in regards to this case.

Best Regards,

Richard Tan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As workaround provided (using a machine with more memory/ code changing/ use Quartus Pro), I will now transition this thread to community support. If you have a new question, Please login to https://supporttickets.intel.com, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

Thank you.

Best Regards,

Richard Tan

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page