- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, i have been trying to test LVDS functionality by creating an output as reg (not wire) and then setting its' val with a non-blocking assignment inside an always loop.

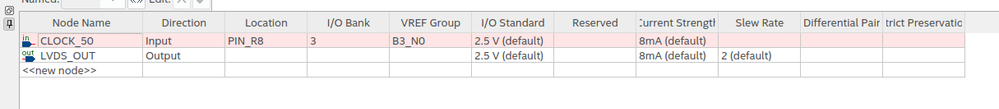

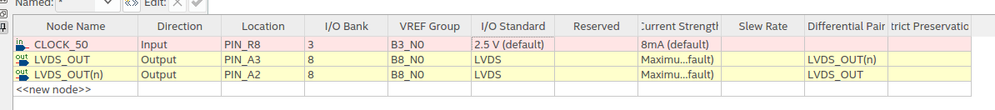

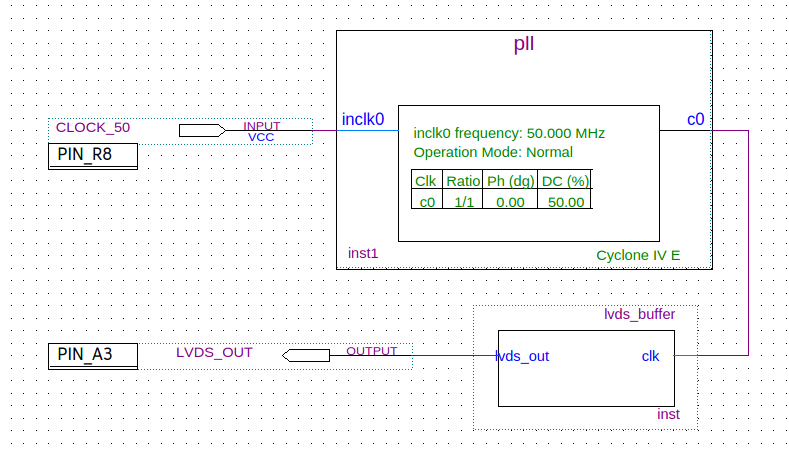

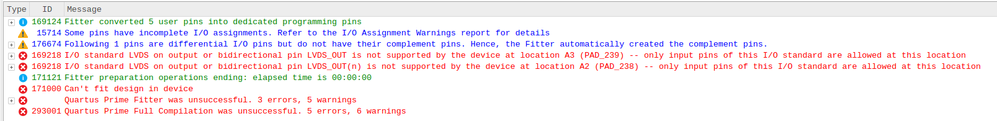

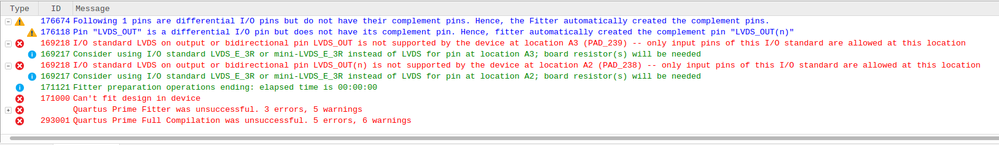

I started by creating a single output called lvds_out. I then created the symbol by running File->Create/Update->Create symbol files for current file. I inserted the symbol in the block-diagram form and run Analysis & elaboration. Then i got into Pin planner and i saw the pin that i created (as i should). As soon as i selected LVDS and hit ENTER the negative output was selected for me. I compiled and i got the error messages that you see in the attached images.

I am obviously doing something wrong. What is the process when creating a LVDS output? Is the logic same when creating LVDS inputs? Should i be having 2 outputs in my verilog (and accordingly in the block-diagram) instead of one?

Can you pls help me out here?

Verilog code:

//It has a single clock input and a 32-bit output port

module lvds_buffer (

input clk,

output reg lvds_out

);

// on positive clock edge

always @ (posedge clk) begin

// Reverse level on every positive edge

lvds_out <= ~lvds_out;

end

endmodule

- Tags:

- lvds

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I obviously forgot to mention that i am using DE0-nano which has a cyclone IV E EP4CE22F17C6N FPGA.

I was able to solve the issue by selecting LVDS_E_3R instead of the LVDS. All i wanted was to just pass the clock to the LVDS output and measure it with my scope.

The error message itself proposed that solution which i saw later on (after posting my first message).

Is this supposed to be a solution? I mean, is it normal for plain LVDS to NOT work as an output?

By the way, what are the chances that the DE0-nano can work with a 500MS/s plugged in on a pcb that i am planning to design?

I know that the DE0-nano pcb is not optimised for that high speed.

I basically have 2 options:

I am designing a 12bit 125MS/s dso with 2 channels (at the moment - 4 ch. latter).

The ADC can transmit (1) DDR data over 6 LVDS-pairs at 250MHz through each dedicated output or (2) use one output to transmit both channels data at 500MHz.

If i choose the first method i have to connect 24 pins between the ADC and FPGA or 12 pins if i use the second method.

I know that terminations and proper pcb design are key elements to minimize reflections and signal distortion.

What do you think, would this work?

If this is a dead end i obviously have to consider including the FPGA in my pcb design which is a headache but i will have to do it.

Your suggestions will be highly appreciated

Thanks and regards

Manos Tsachalidis

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I just tried creating a LVDS input but compiling failed. I used C2 as the positive pin and the pin C1 was auto-assigned by pin planner.

Then i changed C2 level to 2.5V (single ended), deleted the auto-assigned negative pin (C1), tried compiling again and it worked.

So what is it with the LVDS inputs and outputs?

Can you pls describe the process of configuring LVDS inputs and outputs in Quartus? Is there a pdf from intel which describes the process?

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi again, i am very sorry for this but it seems that i have not been doing enough reading. I am at the very beginning of this so please accept my apologies. I have not been using the correct IO banks.

LVDS works fine as long as the correct bank is selected and by saying that i mean that the appropriate pins (that belong to the correct bank) must be chosen.

There is a reference on that in the cyclone IV handbook page 123/490 where the definitions of banks with their supported standards.

Could you pls still try to answer my DE0-nano-related questions?

Thanks and Regards

Manos

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello ,

From the above your reply when you said LVDS_E_3R working then I understood that channel is not differential end pair...I was trying to find part number and pin mapping sheet whether particular channel support dedicated LVDS channel

and you confirmed it is not ..Good

First thing i would give some input about what is LVDS_E_3R..as you said you are at beginning .it is good to learn when you see things " LVDS assignment for non dedicated differential pins as LVDS_E_3R .This standard required 3 external resistors.

I can comment with cyclone IV E LVDS can support around 800 MBPS with provide clock speed.I am not sure about particular board. But i did see few folks mentioned in forum that they tried out and successfully.

Below link is for references

https://forums.intel.com/s/question/0D50P00003yyNgXSAU/lvds-and-de0nano

In the method 2, can you help me to understand how to differentiate the channel ?

Thank you ,

Regards,

Sree

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Are you referring to the 2nd way of transferring the data from the ADC to the FPGA?

The ADC is the ADS4225. Link: http://www.ti.com/lit/ds/symlink/ads4225.pdf

See page 62 where the DDR LVDS output data is described. Both clock edges are used. The output data rate is twice (250MS/s) the ADC sampling rate (125MS/s) because you have 6 pairs that output 12 bits so data must be transmitted on both clock edges in order to do that.

See page 66 where multiplexed output transmission is described. The ADC has 2 channels and in order to transmit both of them through one output it has to double the bit rate from 250MS/s to 500MS/s.

Thanks again for your time.

Regards

Manos

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your message Sree. It's all clear to me now.

Best regards

Manos

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page