- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

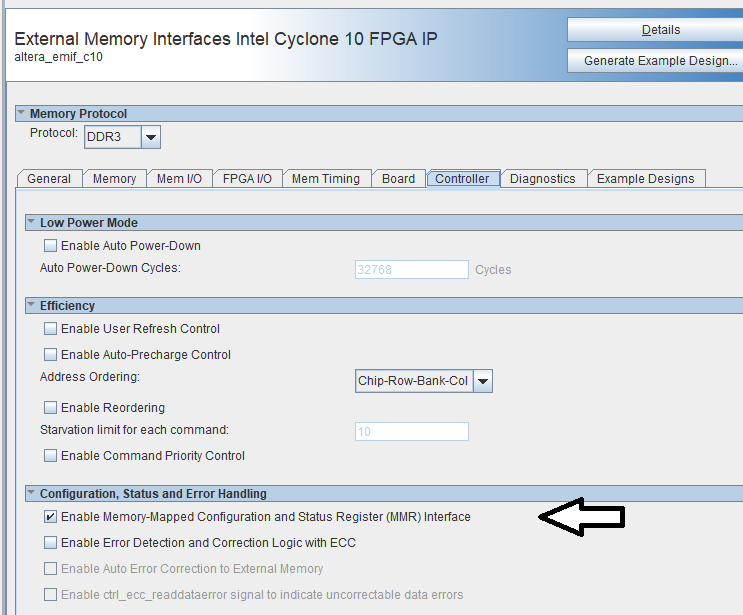

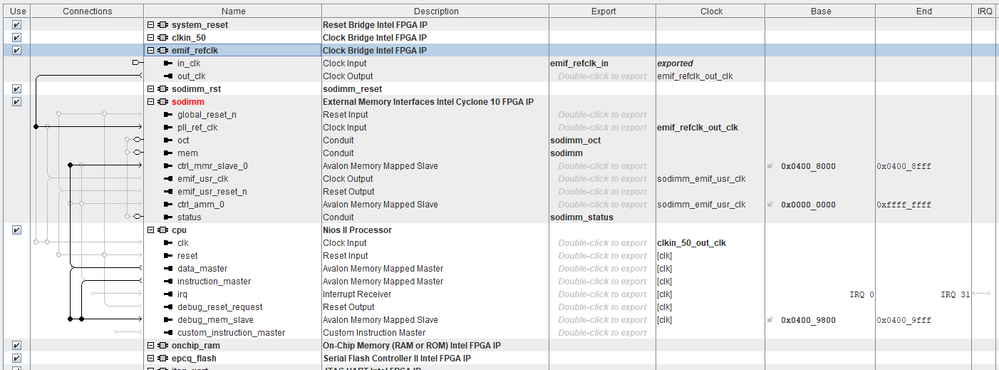

I checked "Enable Memory-Mapped Configuration and Status Register (MMR) Interface" in tab "Controller\Configuration, Status and Error Handling" for External Memory Interfaces Intel Cyclone 10 FPGA IP in Platform Designer for Quartus Prime Pro Version 18.1.1 Build 263.

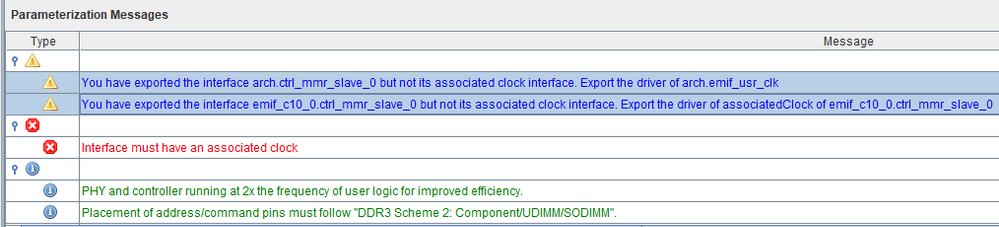

After that I received messages:

Warning: sopc_emif_c10_0.emif_c10_0: You have exported the interface arch.ctrl_mmr_slave_0 but not its associated clock interface. Export the driver of arch.emif_usr_clk

Warning: sopc_emif_c10_0: You have exported the interface emif_c10_0.ctrl_mmr_slave_0 but not its associated clock interface. Export the driver of associatedClock of emif_c10_0.ctrl_mmr_slave_0I don`t understand what I have to do in this situation?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You have the MMR interface enabled, but you haven't connected a clock interface yet (pll_ref_clk). Once you connect the reference clock for the interface, the error should go away.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear sstrell,

Thank you very much for your desire to help me.

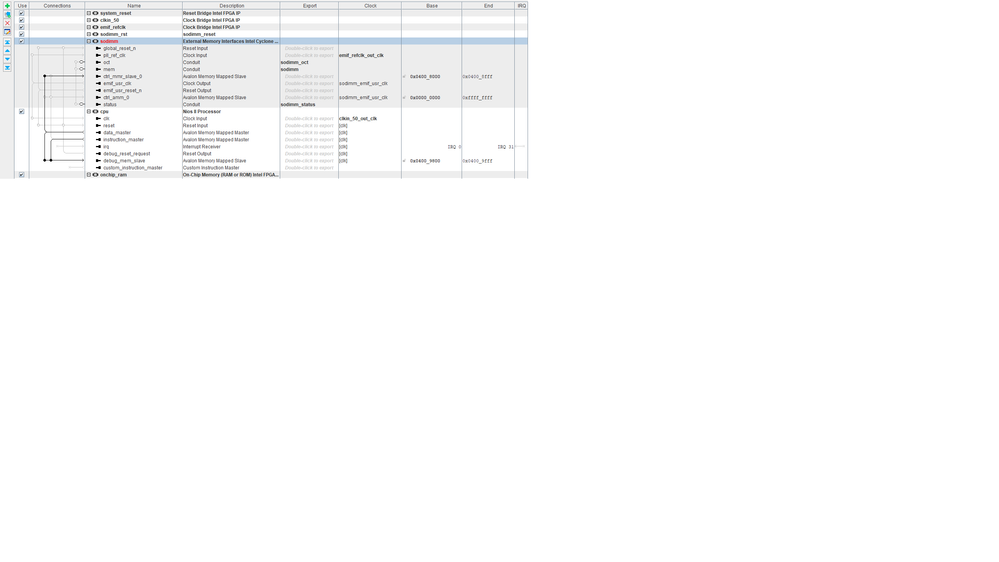

Actually the input "pll_ref_clk" is connected to "emif_refclk" (Clock Bridge Intel FPGA IP). This component is collapsed, but you can see the signal "emif_refclk_out_clk" in the column "Clock".

The project is already working, but the module is very hot and I wanted to switch DDR3 in the deep power-down mode at the time when image generation is not performed. That's why I want to use MMR register for control the deep power-down mode with sideband5/sideband10 addresses. But when I checked "Enable Memory-Mapped Configuration and Status Register (MMR) Interface" nothing inputs added to the "sodimm". And I don`t understand what I have to do in this situation?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

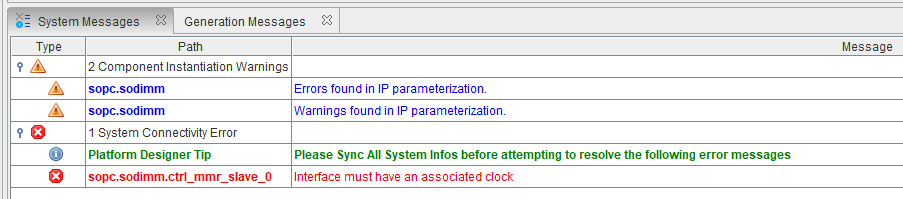

You normally don't have to set the associated clock for an interface on an off-the-shelf IP. The Clock column should be filled in with the associated clock interface in brackets ([ ]) like it is below in your Nios component, so I'm not sure what's going on here.

Since you're using Pro edition, I'd check the Component Instantiation tab and make sure you haven't accidentally changed or deleted the associated clock for the MMR interface.

I'd also recommend going into the EMIF IP's parameter editor again and generating the example design with the MMR option turned on. Take a look at how that project is set up and see if there's anything you need to replicate here in your main project.

Worst case scenario: delete the component from the system and add it back it (re-parameterize). Something has gotten messed up here with the associated clock property for the interface.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear sstrel, many thanks for your advice. I deleted the component from the system and added it back with MMR option turned on. Now everything is fine with MMR register 🙂

Unfortunately, the whole project is in slacks after compilation and now I try to understand why 😕

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Konst_777,

You can try to optimize the timing by change Quartus assignment -> setting -> compiler setting and select one of the performance option under Optimization mode then recompile design again. (refer to page 201 of the EMIF handbook for more details on how to optimize timing)

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-20116.pdf

Hope this helps

Regards,

NAli1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi NAli1,

Many thanks for your advice. It really helped me.

I migrate my project to the Quartus Prime Pro 19.2 in the hope that there will be fewer problems with the new version. Indeed, something has improved. But, new problems have appeared.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page