Hello there ,

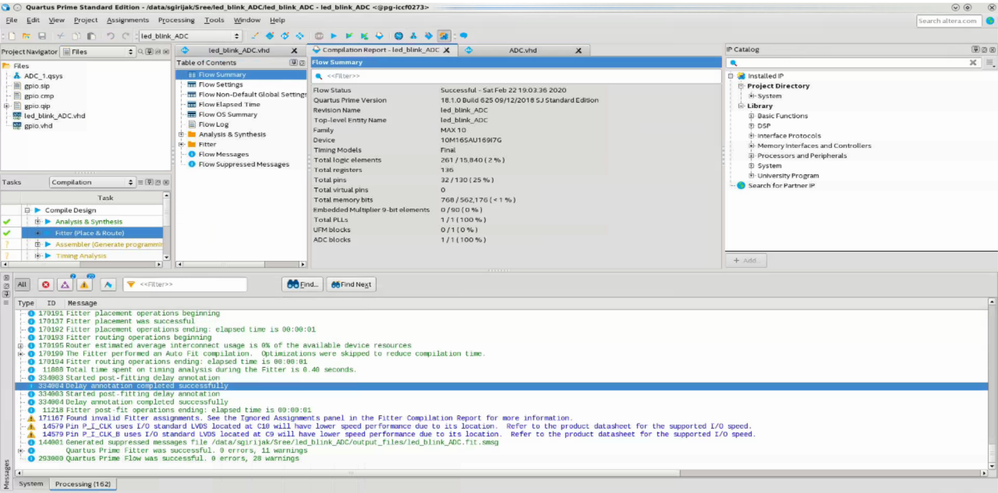

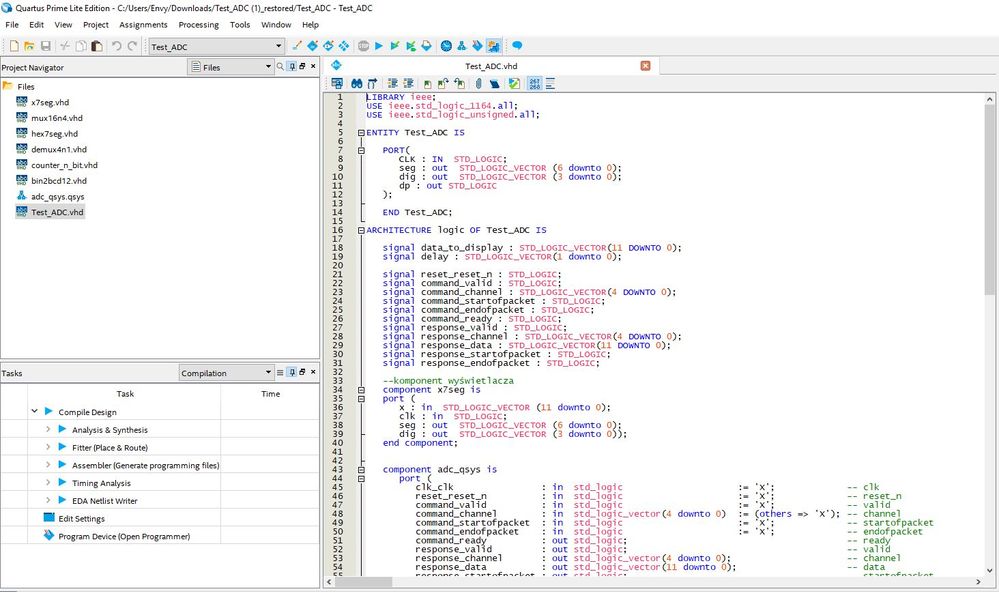

Here attached the screen shot and the modfied design file with ADC block utilization mentioned in the compliation report.

As of understood from the design you provided , quartus is optimizing the ADC block since it is no where used in the design.

In the modified design i instantiated the ADC input and clock as Input port which restrict the quartus to optimize the same.

Hope helps ,

Thank you ,

Regards,

Sree

連結已複製

Hello ,

I get chance to look your design , Looks part you selected is not support the ADC features. Only SA and DA parts supports the ADC. Here is the link for device overview for page 5 mentioned in the part number selection.

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/max-10/m10_overview.pdf

when I open the IP in platform designer, i am getting error as mentioned "Error: max_ADC.modular_adc_0: The selected device part number 10M16SCU169I7G does not support ADC"

Can you use either SA or DA part to use the ADC feature ?

Thank you ,

Regards,

Sree

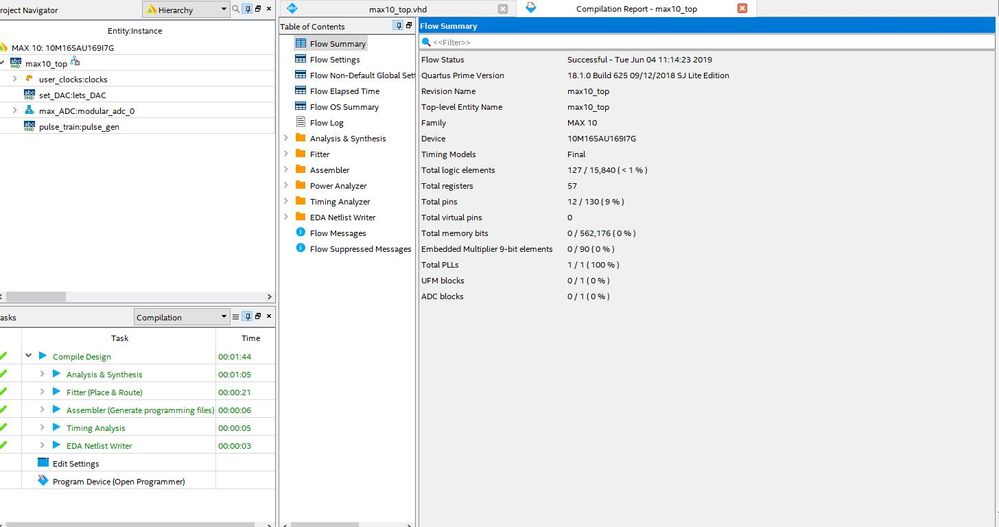

If you look at the above screenshot of the flow summary - it clearly shows a SAU device and also shows the no. of ADC blocks in the device but does not show it as used for the design even though the qsys file compiles!

But the design you send me as per below screen shot , with having error you wont be able to generate the HDL with error in qsys.

which one i should be believe your design files or your screen shot ? please clarify

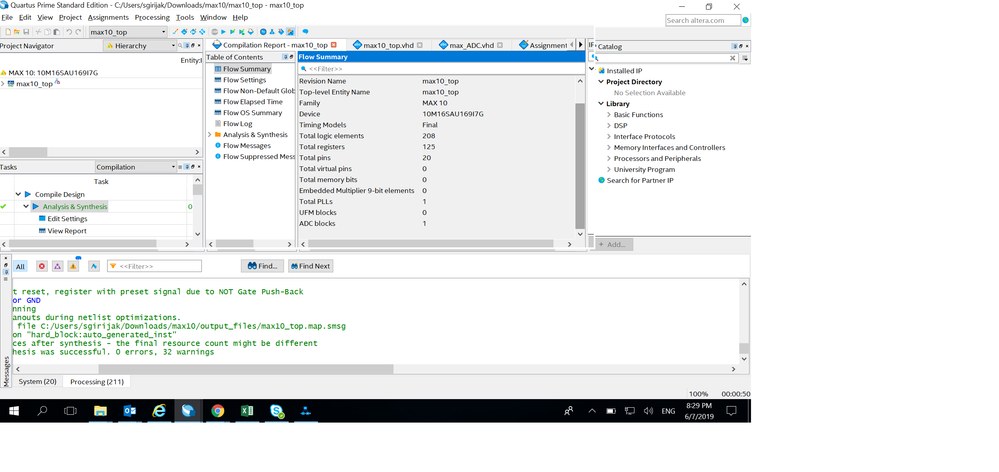

Here is the screen shot of compilation report attached.

One thing I noticed that you dont have a RTL for enable the channel or reading the ADC channels , I added a test logic directly enabled the channel "0" , Channel Valid and Channel start. After that I could see in ADC resources in compilation report. I think since the implemented RTL is not using ADC /enable the ADC Quartus is optimization is not instantiating the module.

Sorry , I dont know how to attach the file here ,Here is the added logic in the top module for your reference ,

command_channel <= "00000";

command_valid <= '1';

command_start <= '1';

command_ready <= '1';

process (P_I_CLK100,response_valid)

begin

if rising_edge(P_I_CLK100) and response_valid = '1' then

data_to_display <= response_data;

end if;

end process;

Thank you,

Regards,

Sree

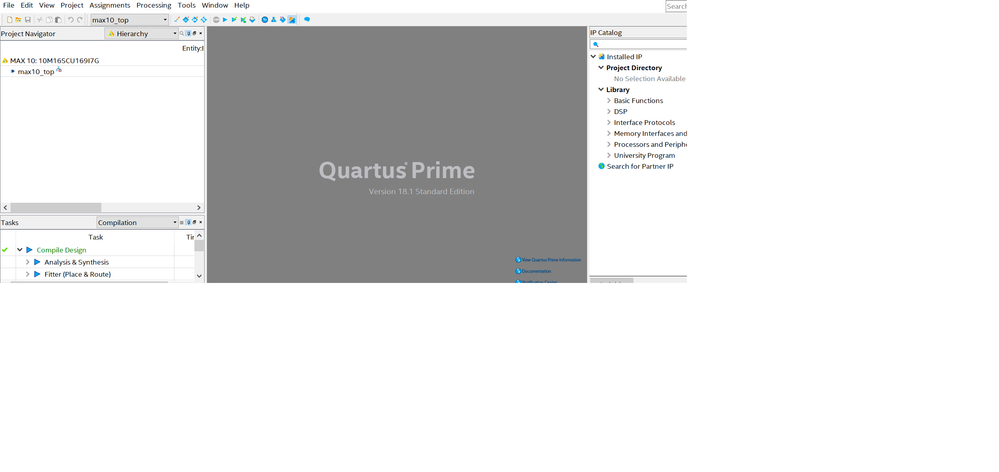

I added the above suggested logic but to no success. I even tried setting up a new project to double ensure the right part selection from the beginning, however I do not see the ADC module invoked neither the addition of the ADC pins in the final summary. Attached is the screenshot and top level module. I hope this is not a Quartus standard versus lite issue? And if the issue is not software related, can you send me the above depicted correctly compiled project+project files from your end?

I added the above suggested logic but to no success. I even tried setting up a new project to double ensure the right part selection from the beginning, however I do not see the ADC module invoked neither the addition of the ADC pins in the final summary. Attached is the screenshot and top level module.

Hi,

This is a project created by a blogger 'maximator' which once I edit to my design plans removes the ADC block for some reason. Can you send the project file specific to this query, please?