- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

From what i can tell the ADC module only needs a command to select which port to sample so how do i make pin assignments to confirm the ADC in use!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello there ,

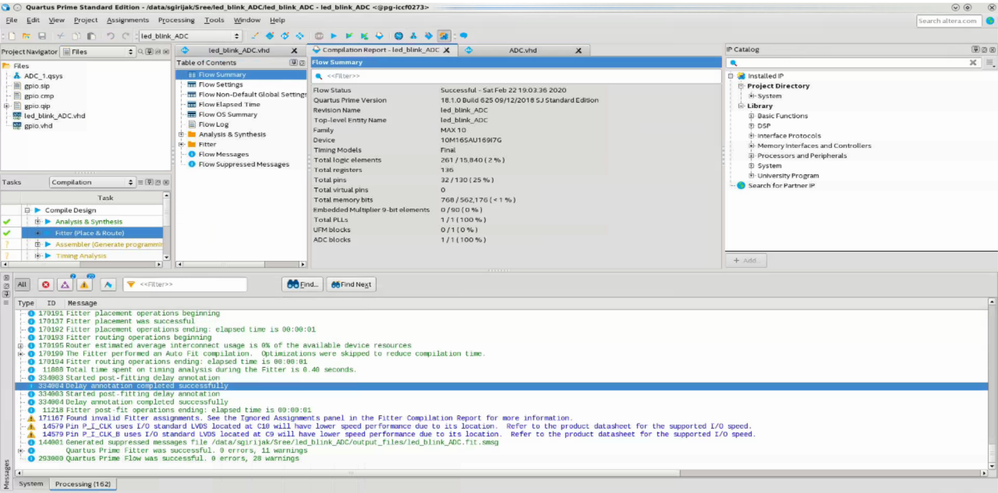

Here attached the screen shot and the modfied design file with ADC block utilization mentioned in the compliation report.

As of understood from the design you provided , quartus is optimizing the ADC block since it is no where used in the design.

In the modified design i instantiated the ADC input and clock as Input port which restrict the quartus to optimize the same.

Hope helps ,

Thank you ,

Regards,

Sree

Link Copied

- « Previous

-

- 1

- 2

- Next »

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

can I know did you get a chance to figure it the issue ? if you still facing the issue kindly let me know ?

Thank you,

Regards,

Sree

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

sorry , didnt see your updated post ; Can I know you still facing the issue ?

Thank you ,

Regards,

Sree

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes Sree, I am still facing the same issue besides I have attached all files you requested in the past. Can you please provide an solution to the above attached project file as soon as possible?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

sorry, i didnt noticed your reply , can i know is that issue resolved ? kindly let me know if you looking for my design files still.

Apologize my delay in response.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello , I thought i attached the file to you , Sorry looks i missed out, Can i know you still facing the same issue ? if yes , i will look at again .

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am still facing the same problem. I have been able to check the ADC input if I invoke the Jtag avalon adapter but if I use just the ADC control core the response data is stuck at zero. In the attached project I am trying a simple led blink check using the output of the ADC module. I would really appreciate a prompt reply.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello there ,

Here attached the screen shot and the modfied design file with ADC block utilization mentioned in the compliation report.

As of understood from the design you provided , quartus is optimizing the ADC block since it is no where used in the design.

In the modified design i instantiated the ADC input and clock as Input port which restrict the quartus to optimize the same.

Hope helps ,

Thank you ,

Regards,

Sree

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello ,

sorry , I completed missed that your case here.

can you let me know you still facing the same issue , if yes I can attach the design which another customer posted the same in fourm.

Thank you ,

Regards,

Sree

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »