- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Some asynchronous need to use LCELLs to generate pulses, like following example.

However, the delay of LCELLs is different on the difference FPGA device.

So, I use following constraints to constraint the min delay of LCELL.

But it doesn't work.

How to constraint min delay between LCELLs?

Thank you very much.

Ex.:

lcell dly1d (.out(y1), .in(A) );

lcell dly4d (.out(y), .in(y1) );

Constraints:

set_min_delay 5.0 -from [get_pins dly1d|combout] \

-to [get_pins dly4d|combout]

set_net_delay -min 5.0 -from [get_pins dly1d|combout] \

-to [get_pins dly4d|combout]

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Right so I don't think this constraint works on LCELLS alone. Because you would need a setup/hold relationship in the first place.

Which brings us back to using set_data_delay, which definitely should work on LCELL alone.

Since it isn't supported on Quartus II 13.1, I suggest you migrate to Quartus Standard 21.1 as this would have the set_data_delay.

On the other hand, you are using LCELL to generate a pulse to wake up the clocks right? Maybe you could consider using clock control IP: https://www.intel.com/content/dam/support/jp/ja/programmable/support-resources/bulk-container/pdfs/literature/ug/ug-altclkctrl.pdf

Regards,

Nurina

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For minimum delay between, you would have your -from point to the output of one and your -to point to the input of the next. You're pointing both to the outputs of both.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sstrell

Thank you, sstrell, very much.

How to know the LCELL's input after quartus synthesis for pointing the input to -to?.

Thank you very much.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, does the above reply help?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Nurina

Thank you, Nurina, very much.

How to know the LCELL's input after quartus synthesis for pointing the input to -to?.

Thank you very much.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The easiest way is to use the Name Finder, accessed when you use one of the GUI dialog boxes to create a timing constraint. You can access them if you have your .sdc file open in the Quartus text editor (Edit menu -> Insert constraint).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sstrell

Thank you, sstrell, very much.

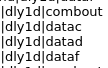

The Name Finder find signals of LCELL dly1d as follow picture. Which one is the input of the LCELL dly1d?

Thank you very much.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The data ports are the inputs. You can also look in the post-fit Technology Map Viewer to see these in a schematic view.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sstrell

Thank you, sstrell, very much.

I change the constraints to which are as follows.

Constraints:

set_min_delay 0.8 -from [get_pins dly*d|combout] \

-to [get_pins dly*d|data*]

set_net_delay -min 0.8 -from [get_pins dly*d|combout] \

-to [get_pins dly*d|data*]

After Quartus compile done, I report the relative path. The report command is as follow.

Report command:

report path -from [get_pins dly1d|combout] -to [get_pins dly4d|combout]

I saw the report. The net delay result isn't extended.

Does there have any problem of constraint setting?

Thank you very much.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Does any one know the root cause? Please help me. Thank you very much.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Apologies for the late response, I was on vacation.

Can you share your design so that I can reproduce the problem from my machine?

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Nurina

Thank you, Nurina, very much. You may enjoy your vacation first^0^.

My design is as follows. I use LCELL to generate a pulse in a module without a clock.

The design will be implemented on the advance node FPGA device, and it can't be modified.

On the advance node FPGA device, the delay of LCELL becomes shorter.

If the slew rate of A is too late, it may cause the generated pulse to fail.

So, I want to constraint the min between A and Y4.

I try to constraint the min delay between LCELLs, but it fail.

Design:

lcell dly1( .out(Y1), .in(A) );

lcell dly2( .out(Y2), .in(Y1) );

lcell dly3( .out(Y3), .in(Y2) );

lcell dly4( .out(Y4), .in(Y3) );

wire pulse = A & ~Y4;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Is there any reason why you don't want to create a pulse using flip flops? I don't think it's a good idea to create a pulse using LCELL primitive, its delay depends on hardware variables, so race conditions may happen thus creating an unreliable circuit: https://www.intel.com/content/www/us/en/programmable/quartushelp/17.0/hdl/prim/prim_file_lcell.htm

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Nurina

Thank you, Nurina, very much.

Using LCELL to create a pulse is an unreliable circuit.

But the original SoC design has a sleep mode that all clocks are closed.

During that mode, I can only use LCELL to create a pulse to wake up clocks.

So, I need to constraint the LCELL delay to make the pulse width more robust.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

May I know which version of Quartus you are using? and which device are you using?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Nurina

Thank you, Nurina, very much.

I use Quartus13.1, and the used devices are Stratix III, Stratix IV and Stratix V.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Could you try set_data_delay instead of set_net_delay? I believe this should take place as you are using LCELL.

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Nurina

Thank you, Nurina, very much.

Unfortunately, Quartus13.1 seem that don't support set_data_delay command.

Have any others command can instead of set_net_delay?

Thank you very much.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry about that, set_data_delay is pretty new in TimeQuest. I think the best you can do is use set_min/max_delay if you want to use LCELL. These two constraints would override default setup and hold relationships so your specification should be able to take place.

You may find this forum thread useful: https://community.intel.com/t5/Programmable-Devices/set-max-delay-vs-set-net-delay/m-p/232670

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Nurina

Thank you, Nurina, very much.

I had tried following constraint to limit the min delay between LCELLs to more than 0.8 ns.

But it fail.

After compiling done, I report the path delay in TimeQuest, which is from the LCELLs output to another LCELLs output.

The delay time still small than 0.8 ns.

Constraints:

set_min_delay 0.8 -from [get_pins dly*d|combout] \

-to [get_pins dly*d|data*]

Report command:

report path -from [get_pins dly*d|combout] -to [get_pins dly*d|combout]

Design:

lcell dly1d( .out(Y1), .in(A) );

lcell dly2d( .out(Y2), .in(Y1) );

lcell dly3d( .out(Y3), .in(Y2) );

lcell dly4d( .out(Y4), .in(Y3) );

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Right so I don't think this constraint works on LCELLS alone. Because you would need a setup/hold relationship in the first place.

Which brings us back to using set_data_delay, which definitely should work on LCELL alone.

Since it isn't supported on Quartus II 13.1, I suggest you migrate to Quartus Standard 21.1 as this would have the set_data_delay.

On the other hand, you are using LCELL to generate a pulse to wake up the clocks right? Maybe you could consider using clock control IP: https://www.intel.com/content/dam/support/jp/ja/programmable/support-resources/bulk-container/pdfs/literature/ug/ug-altclkctrl.pdf

Regards,

Nurina

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page