- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi everyone,

Environment : WIN10 64bits, Quartus II 18.1, modelsim-altera 10.5b, cyclone V E 5CEFA9F31I7N, Micron MT41J128M16JT-125*2.

I am a FPGA beginner. In my design, I used two Micron DDR3 on the PCB, I configured the IP core correctly, wrote a simple read and write test program, and verified it with Signaltap on the actual PCB, so I can sure that I can control DDR3 properly.

Now I want to use modelsim for RTL simulation because my code logic becomes more complex and signaltap sometimes doesn't reflect all timing situations better. But I don't understand how to do RTL simulation. I write a testbench, but modelsim show me some errors, for instance: modelsim Module parameter 'CFG_CMD_GEN_OUTPUT_REG' not found for override.Do I need to add some model files?The "External Memory Interface Handbook" has a lot operation to offer. but I can't find a specific operation.

Can you list the necessary steps? I want to follow these steps to complete the RTL simulation.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You'll want to create the simulation example design from the EMIF UniPHY IP by running the scripts generated. I'd link you but it appears a number of pages are down on intel.com right now.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello and Good Day,

In my opinion, you can create an example design from the EMIF IP.

And then you can a run a simulation with a Modelsim script.

You might want to refer to the link below for a reference: https://www.intel.com/content/www/us/en/docs/programmable/683841/17-0/functional-description-example-designs.html

Thanks,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Adzim,

Thank you for your reply!

In fact, I used other methods to finish the simulation of modelsim. This method requires me to configure the simulation environment of modelsim correctly, write msim_setup.tcl scripts, .do files, etc. This method is very complicated, and in the process of simulation, the initialization of DDR3 can be successful, but the avl_ready signal will become unknown status after a period of high level. The problem may be that the timing I wrote is wrong, or the configuration environment is wrong. The most important thing is that all the work is done in the modelsim environment, and I still don't know what method to use to reliably complete the modelsim simulation after I wrote my own top-level file and testbench file in quartus. Which script do I need to run?

Thanks,

Ryan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ryan,

When generating the example design, you can choose either synthesis or simulation or both of them.

Then the Quartus will generate the design accordingly.

For the simulation file, the Quartus will generate a tcl script for each simulator.

The script should has the library for the initialization and calibration flow of the DDR3.

You can run the generated script to test the design.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Adzim,

Thanks for your reply!

I already kown that how use modelsim to do RTL simulation of DDR3. In fact, I can directly use the RTL simulation of quartus Nativelink, but I need to revise the of .do files. Just refer to this link:https://www.macnica.co.jp/business/semiconductor/support/faqs/intel/134865/

Regards,

Ryan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

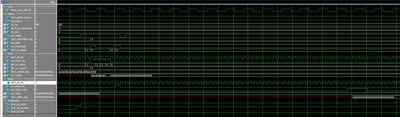

Supplement: In modelsim, you can see that I correctly store the data according to the timing requirements, the read data is always 0. but the data can be correctly retrieved in the Signaltap test.Do you know the possible reason?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ryan,

Thanks for your feedback.

I'm not sure what is the reason for that but maybe you can perform a burst transfer of 4 and see if there is any different.

What is the ddr3_wr_state signal represent in here?

What is the different between the ddr_wr_count and ddr_wr_count1?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We do not receive any response from you to the previous question/reply/answer that I have provided. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page