- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Linux Qsys Now "platform designer", from old time still has trouble never addressed.

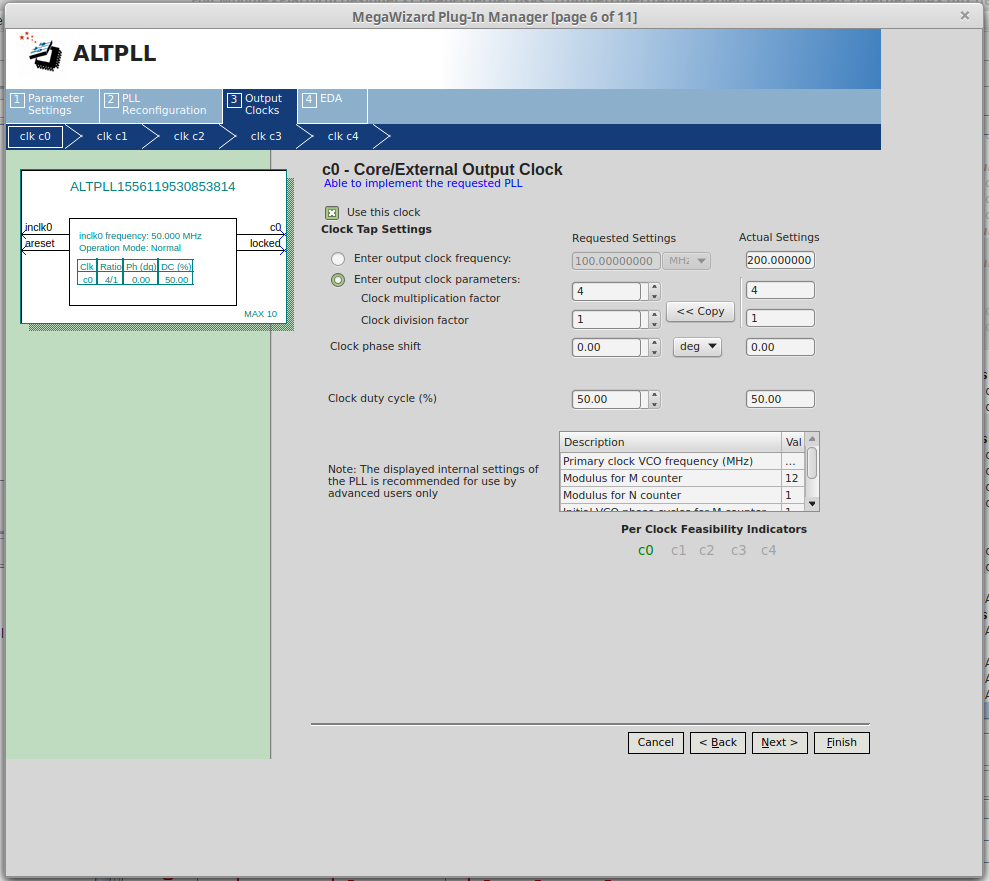

ALT_PLL Altera FPGA IP open in a small window with scroll bar, if something is touched in this state after long time crash.

If enlarged scroll bar disappear and PLL can be edited but again doesn't save.

This trouble is present till version 15.0.

Tcl file is messed up and unreadable.

The only way to use PLL on linux platform is to import old PLL file then edit parameter by hand.

Attached actual file I patched to generate Frequency I need on my design.

When opened for edit all parameter are set in different unit and still try to save leave untouched.

How can I cure this unpleasant issue?

Linux Mint release 17.2

Intel I7, Sony Vaio Pro SVS1511C5E 16GB ram.

As oon picture crash.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

When enlarged as shown just save if one clock output is selected (sometimes) again editing never succed and next open show new parameter not held.

After succesful add I try'd two times add 3 more clock for 200, 250 and 10MHz, changes never appear on .qsys file.

Project is shareable just removing two IP core.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

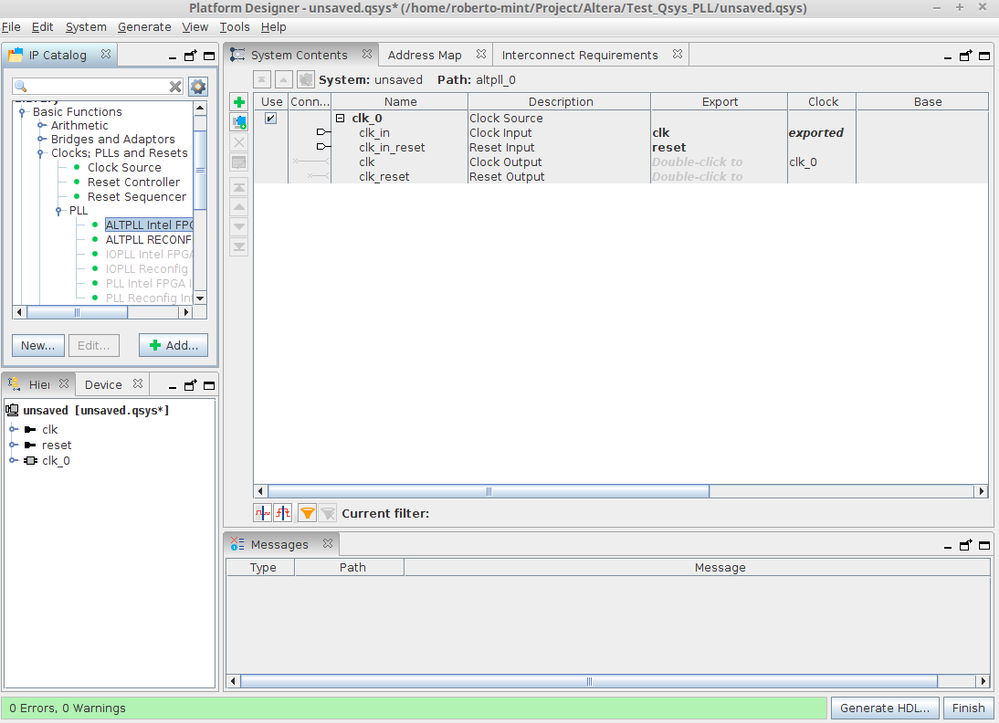

I'm not sure why the old Megawizard is showing up in a new version of Quartus. I'd recommend simply deleting the PLL component from your system design and re-adding it.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sstrell, this issue as I wrote is still present from revision 15.0 When I learned how to write My Ip core modules.

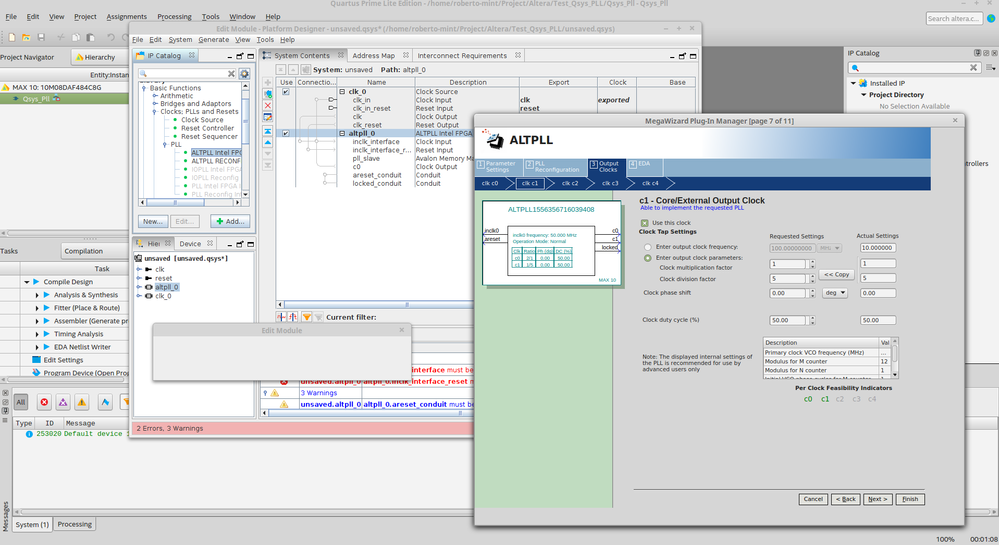

Also in a new design if I add ALT_PLL has same behavior. See this

Enlarge, edit parameter then finish

Finish result in not saved PLL

Step 3 add ALT_PLL, enlarge then two times finish button.

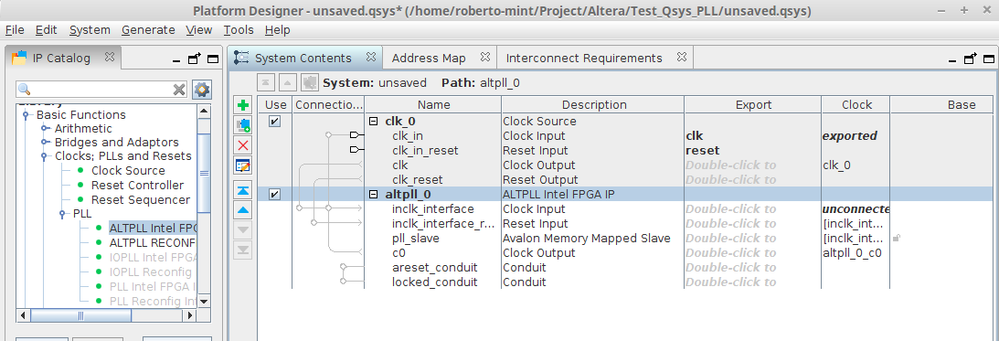

step 4, edit Alt_PLL, just configure clock input 50MHz, C0 to 100MHz, c1 10MHz as from step 2, finish finish and IP remain as is from step 3.

Delete add again same deterministic sequence. Alt_PLL_Reconfigure has same issue, other IP work like a charm.

This as I stated never changed from at almost revision 15.0, I had no previous revision installed,

Regards

Roberto

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi RSree, test on Linux? I am not interested about Win, too slow and unreliable.

Again a base project, generate PLL saving as is no edit allowed after create.

It is not working and I see this problem also on other distribution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Rsee, I loaded the file you sent back, I argue is just same I sent you.

Please OPEN QSYS (Platform Designer) LINUX version and try modify PLL settings:

Input clock 50MHz not 100

C1 Clock need a multiplier 2

C2 clock need a divider 5 to output 10Mhz clock

C3 ex set to 200MHz require a multiplier 4.

DSave and reopen, check change are on file.

If you can setup on Linux, and send back, then and only then you tested issue.

Quartus installed on Ubuntu 18.02_4 doesn't work so I cannot test till now.... I open another issue soon.

regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi RSree, sorry for what I have to write:

Are you an FPGA designer and proficient on HDl languages, Platform designer usage?

Why I am asking this? I feel as you are VERY far from what happen, from how a PLL work and never checked reconfigure PLL clocks input and PLL section feedback counters.

Issue is about some TCL error I cannot address, Verilog VHDL is just the generated design hardware.

Openiing the design file by hand then set the PLL block, refresh design and then load with all clock, generate correct IP core. Platform designer provided interface DOESN'T WORK!!! INTERFACE, SOFTWARE ISSUE, not HDL generated file.

See snapshot, see what happen to saved PLL has just one clock C0 is on module, where set up C0, C1, C2, input frequency is not 100MHz default MUST BE 50MHz, Optput need be what I select and MORE THAN ONE I repeat REPEAT C0, C1, C2...

Software code messed up is graphic interface, if you open is stretched and if you touch something it crash after a while. Resizing doesn't crash but NEVER save chenges on QSYS file. File is quite messed up.

About dummy Master, this is another point I fear you are far from HDL design, is a very simple useless module to quiet warning and silence bus when no controller are there.

Is very simple to "add new" from left ip core selector one just by new component then import vhdl file.

This missing tcl file ( I can setup on project and send you) is not affecting the culprit of issue YOU CANNOT EDIT NOR APPLY AND SAVE CHANGES TO PLL PARAMETER!!!! THIS FROM 15.0!!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

I totally understand what you are trying to say, and able to understand the dummy block . My intension only want to show you that the Qsys file is not generated successfully with the design that you send.

Again with Verilog, we had an issue on certain versions between Verilog and VHDL languages . So only to isolate the language issue I have suggested the above procedure.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, I know this is quite an old thread, nevertheless I have the exact same problem with the Platform Designer. I tested versions 18.1 and 20.1 (Standard edition) with the exact same behavior. It is not possible to add an ALTPLL component in the Platform Designer. The wizard appears (you then have to resize it, otherwise it will crash), you can make your adjustments an when you click finish nothing happens, no error message nothing.

When opening a QSYS file that already contains a PLL, it is possible to open the settings (i.e., the Mega Wizard) but changes have no effect.

Is Quartus under Linux. Are there any suggestions how to work around this problem?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You probably should start a new thread on this.

New components get added to the bottom of the System View (System Contents). You don't see it anywhere and no messages in the Messages window about it?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The issue is that qmegawiz command returns with status 1 which means "Cancel", so the tcl interprets the result as the user had clicked "Cancel" instead of "Finish". As a dirty hack I changed the following line

if { $status != 0 } {

to

if { $status != 0 && $status != 1} {

in ~/intelfpga_lite/20.1/ip/altera/sopc_builder_ip/altera_avalon_mega_common/sopc_mwizc.tcl

and it works. The "Cancel" button doesn't work after this of course but it's a far smaller issue.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Good hack, @ghanko! There are a couple instances of the line you mention in the file you mention. The diff on the file is below. I applied the patch and got past the problem that others are seeing:

[gregh@Autolycus altera_avalon_mega_common]$ diff sopc_mwizc.tcl sopc_mwizc.tcl-orig

1050c1050

< if { $status != 0 && $status != 1} {

---

> if { $status != 0} {- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm on Quartus Prime Lite 23.1 on Linux, and this ALTPLL Altera FPGA IP module (now called ALTPLL Intel FPGA IP) still does not work. Using the hack mentioned here I can get get the wizard to create it, but I cannot configure it. Any time you get to the (3) Output Clocks page, the wizard crashes. The hack seems to keep it from aborting and deleting it, but there's no way to configure the clocks.

This is a major bummer... it seems to be unusable. If anyone knows how to get around this so the output clocks can be configured... I'd greatly appreciate it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@Serqetry, last year when I posted the above, I was working on the University of Colorado Boulder's FPGA specialization on Coursera. A couple things I learned. Ultimately, Altera (now Intel) do not do a good job of supporting Linux. They just don't. Other tools within the Intel tool chain became maddeningly difficult to get work (if ever) under Linux. Don't even getting me started on Nios. In the end, I spent days of time trying to get Linux to work. Honestly, I switched to Windows. And, Windows just worked. If you have the option to switch to a Windows PC with Intel tools, I would. If you don't, you're going to face an uphill battle as this is will likely be the first of many challenges. I know this doesn't answer your question. But, I wouldn't wish my journey last year (before I switched to Windows) on my worst enemy. Sorry.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the reply! I'm taking the same Coursera courses now, so that's one reason I ran into the exact same problem as you. I know what you mean, Linux usually gets way less attention than Windows, but honestly I'm super grateful Quartus Prime and the other tools are supported on Linux because I'd rather quit computers and electronics and take up botany than daily drive Windows. I do keep a Windows VM around for the situations where something just won't work otherwise... but honestly my biggest complaint with the Coursera stuff is that classes are so horribly out of date. Quartus Prime 16?... why do they not update these courses? I'm amazed I've been able to get this far with the newer versions of Quartus, There's definitely been some ancient crusty file compatibility issues but that's Coursera's fault. You may be right and I'll run into even more trouble in the later courses, so I'll keep that VM on standby and try to not struggle too much. Thanks for the heads up.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm actually on Quartus Prime Like 23.1 for Windows and the same exact thing happens here (so it's not just a Linux issue).

I applied the modification above (the file was located in C:\intelFPGA_lite\23.1std\ip\altera\sopc_builder_ip\altera_avalon_mega_common )

but it did not help

You can get to the PLL Reconfiguration but when you click Next, the wizard closes and the PLL you were building disappears from the design.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm on Quartus Prime Lite 23.1 on Linux too, on the same Coursera class. I managed to configure the clocks by attaching gdb to the wizard, setting a breakpoint on the crashing function, and forcing return of two frames always when it gets called.

First, to enable attaching gdb to a running proces, run as root:

# echo 0 > /proc/sys/kernel/yama/ptrace_scope

Run the PLL wizard from Quartus. In a separate terminal, find the PID of the wizard process (the number from the second column):

$ ps aux | grep mega_altpllq

Attach gdb to it (substitute the proper pid), set up a few things, and resume the wizard:

$ gdb -p 260525

(gdb) set confirm off

(gdb) br _ZN27ALTCLKLOCK_CLK_SETTING_PAGE29should_enable_disable_controlERK10UI_QSTRING

(gdb) c

Proceed with the wizard. When switching to the (3) Output Clocks page, or on any modification of the data therein (which you need a handful of times), the breakpoint triggers. Switch to the terminal with gdb and do

(gdb) return

(gdb) return

(gdb) c

When you're done with the wizard, you can exit the gdb and close the terminal.

I also applied the change to the if in the .tcl file. I don't know if it's needed.

I agree with the sentiment that this is a fun class and that the tooling is a huge pain.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page