- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, I prepared a lot more of issue but I am weakened about...

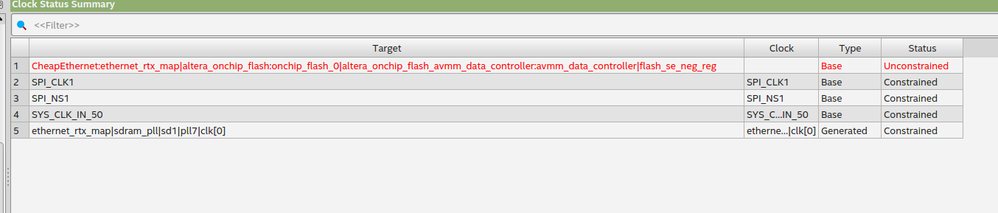

This one is really out of my control:

On chip flash clock is attached to pll C0 as all peripheral are. In same pane, 1 and 5 share same clock, so why this error?

QSYS or Quartus? (Release 18.1 Lite Linux Hosted.)

Same behavior on Win7 version.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

There is one KDB about this. Can you try the workaround stated in https://www.intel.com/content/altera-www/global/en_us/index/support/support-resources/knowledge-base/tools/2016/warning--332060---node---alteraonchipflash-onchipflash-alteraonc.html?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi YY, yes seems solve issue but not side effect. We can address this and other after fair event is coming too soon to experiment.

This issue appeared @2016, is still present.

Dear Intel remember we are not M$, we cannot sell defective product nor we can risk defect on industrial environment where mechanical part with dangerous energy get controlled by silicon.

Too few I think are interested about M$ IOT, think also what happened to smart phone market, few customer buy from a great brand it was Nokia.

My colleague use Linux or Mac as platform, few use windows.

Altera was a great company, why drive to dead end?

Regards.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page