- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

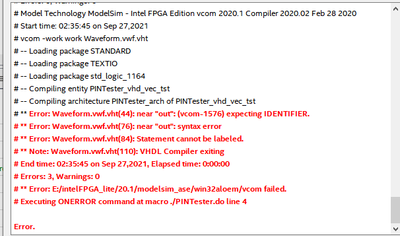

I cannot get a proper waveform simulation for a project. I am running Quartus Lite 20.1. I have a larger project, but I opened a more basic sub-project in order to rule out some issues. I create a file/block, open up the VWF simulation, input the nodes, generate the modelsim/testbench script, and hit functional simulation. I get the error shown in the first image labeled "error" every time. The line it is referencing is shown in the second image labeled "errorline"/

This file does not exist. I have searched every folder related to Quartus and beyond. Everything compiles just fine, and I can upload it to the FPGA where it runs like a dream. I cannot simulate it. I hope someone can say it is something simple, so I can feel stupid and get on with my work. If this has already been solved or there is a better place to ask please point me to it. Thank you for taking the time to read this!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

That file is mainly used for power analysis. Do you want to do any power analysis? Did you try deleting your simulation files and repeat all the steps to start an RTL simulation on university program?

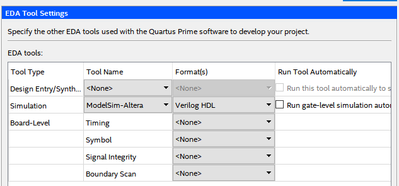

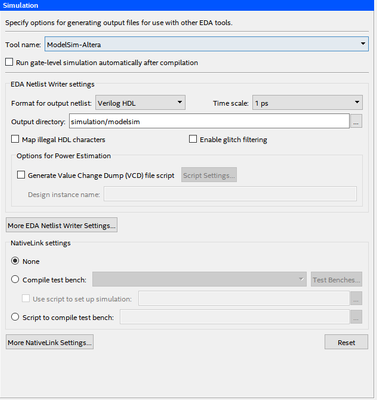

Can you share a screenshot of your EDA settings?

Thanks,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi and thank you for your response!

I don't want to do any power analysis, but how would I get around it? I want to use the vwf simulation, but that file is stopping the functional sim. I ran the RTL simulation tool, but I am not familiar with it. It gave no errors if that is an indication of anything. I have also included a screenshot of everything under the EDA settings in the options. I feel as though it has something to do with the board level section, but I am not sure. In class we simply generated a netlist, assigned nodes, and ran the simulations without issue. That is why I am confused here. Thank you again for your help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your response. Did you run a full compilation of your project on Quartus before running the simulation? Make sure you compile it first.

Otherwise, why don't you try delete the db folders from your project and start a new simulation? If that does not work, try changing your EDA settings from "Modelsim-Altera" to "None" so that the RTL simulator will choose automatically.

Let me know if this helps.

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I did run a full compilation before running the simulation. The compilation is successful, though there are 93 warnings.

I have tried deleting the db folder and starting a new simulation. I did not change the EDA settings. I do believe this has given me new errors which is nice as it is hopefully a sign of progress.

Now, you're talking about the RTL simulator, but I want to do a vector waveform simulation. Are these connected? Sorry I do not know exactly how things are related in Quartus.

I have attached the "new" errors below and I will look into them more tomorrow, but for now I must sleep.

Thank you again for your continued help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

RTL simulator is a simulator that captures the expected Register-Transfer Level behaviour of an FPGA design, which is what the Quartus University Program VWF does. So yes, they are connected.

From your error I think the problem is you named your signal "out", and this is illegal in VHDL/Verilog as that is a reserved name. Try renaming it out1 or anything else, I think that should solve your problem. BTW "in" is also a reserved signal name.

I think you designed your project using .bdf right? The downside of this is that Quartus will compile it as .bdf design, and show you a clean compilation based on bdf rules. But the University Program will convert the design to VHDL/Verilog code first, and then make a testbench based on the code and run the simulation for you, here it will compile the files using VHDL/Verilog rules and you will see the errors here.

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I do not have any pins labelled as "out" or "in". Maybe something is happening with the IP files I do not know.

I need to get actual data from this as deadlines draw near. I will learn the RTL simulation tool and hope it works.

If all else fails I will manually test the outputs in stages through an oscilloscope or do a fresh install and start over.

Thank you for all of your help and maybe at some point I will figure it out. After this project haha

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This may be a dumb question, but do all the blocks in a diagram need to be the same language type? i.e. all verilog or all vhdl? or does it not matter if they mix.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I believe they need to be the same. You must have only one language in a file.

You can have files of different languages though. As in, you can have 2 verilog design files and 3 vhdl design files in a project and it will be fine.

Can you attach your .qar file so I can see what's the problem? To generate a .qar file, go to Project>Archive Project.

Thanks,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We did not receive any response to the previous question/reply/answer that I have provided, thus I will put this case to close pending. Please post a response in the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you with your follow-up questions.

Regards,

Nurina

P/S: If you like my comment, feel free to give Kudos. If my comment solved your problem, feel free to accept my comment as solution!

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page