- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear community,

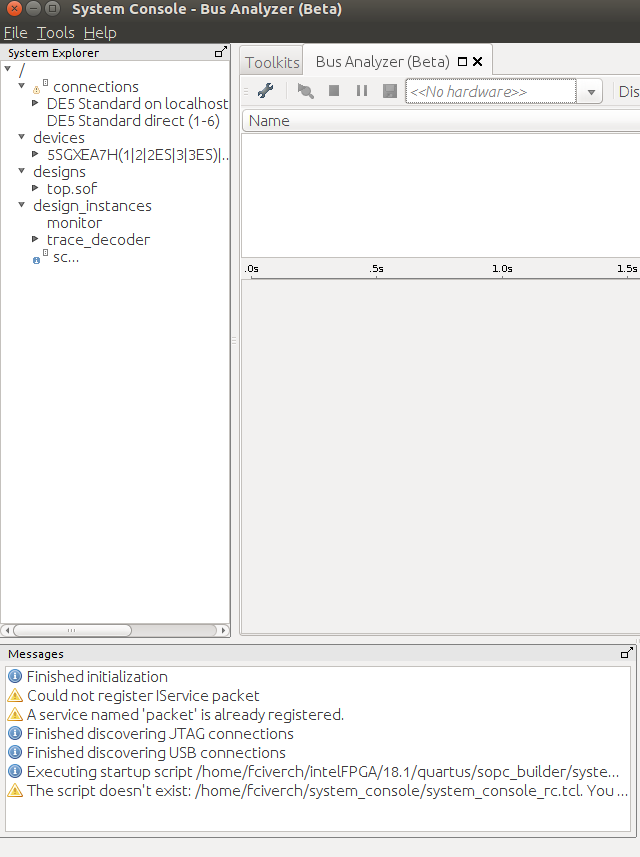

I have a Terasic DE5-Net FPGA based on Stratix V FPGA. I would like to monitor the Avalon MM bus by mean of the Bus analyzer toolkit. I followed the guide of this link (https://fpgawiki.intel.com/wiki/Bus_Analyzer_Toolkit) and I instantiated the analyzer in the Platform Designer. Then, I compiled the design and I programmed successfully the FPGA.

Unfortunately, after launching the beta bus analyzer from system console, I can see the JTAG interface link and the monitor instance on the left menu of the tool but no hardware is detected (see the figure below).

Could you please explain me why no hardware is detected even if the JTAG can program the FPGA?

I tried the bus analyzer tool with another design for MAX10 FPGA but I experienced the same problem. Do you have some ideas?

Thank you.

Best Regards,

Federico

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear YL,

Thank you for your answer.

Yes, there is no .tcl file loaded by the tool. Do I have to add? If so, which commands do I have to write inside the .tcl script to establish the communication?

Thank you.

Best Regards,

Federico

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You don't show it, but did you enable bus analyzer use for particular interfaces in the Interconnect Requirements tab for the system?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear sstrell,

I did not enable the instrumentation in the Interconnect Requirements tab. After your answer, I enabled it from platform designer (I set "TRUE" for "Enable Instrumentation" under "Interconnect Requirements") but the bus analyzer is still showing "no hardware" (of course, I recompiled the design after the changes). Do you have other ideas?

Thank you.

Federico

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Did you add the JTAG Debug Link component as mentioned in the Wiki?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I use the 18.1 version of Quartus and, as described in the guide, from version 14.1 "JTAG Debug Link is auto-instantiated and is not a selectable IP core from the IP Catalog".

Thus, I did not add anything in the design and I only enabled the instrumentation.

Do I have to add something else in the design?

Thank you.

Federico

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I did not write that I would like to monitor the avalon bus of a qsys subsystem. Thus, the signals that I would like to monitor are present in the subsystem interconnect requirements tab but they are not present in the interconnect requirements tab of the top instance of qsys hierarchy. Could this be the problem?

Thank you.

Federico

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have noticed that, after HDL generation in the platform designer, the report gives me the following warning for all the slaves that I considered:

Warning: Cannot insert performance monitor for sysid_qsys_0.control_slave because it only has one connection. Add more connections to allow monitor insertion.

In the Instrumentation tab, I have added one master MM and many slaves MM connect to the same master MM. While the master monitor seems to be ok, I have the above warning for all the slaves.

What am I missing? Do you have any idea?

Thank you.

Federico

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have not tried this with a hierarchical system design, so I'm not sure if that is the problem.

As for the warning, the monitor is most likely on the master side (single monitor monitors all transactions to/from that master), so there's no reason/need to add these extra monitors.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page