- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

i am exploring PLL in zero delay buffer mode and i have 2 CLK outputs. I notice my code past elaboration but failed for

"Error (13076): The pin "PLL_DRP_IP:PLL_DRP_IP_INST|PLL_DRP_IP_0002:pll_drp_ip_inst|altera_pll:altera_pll_i|fb_iobuf.fb_iobuf_ibuf.DATA[0]" has multiple drivers due to the always-enabled I/O buffer "zdbfbclk"."

Is there anything i did wrong? do enlighten me.

Here are my simple code:

module PLL_DRP(

input REFCLK,

input RESET,

output outclk_0,

output outclk_1,

output reg outclk_fb,

output reg sel,

output locked

);

always @ (posedge REFCLK)

begin

if(RESET) sel <= 1'b0;

else

begin

if(sel==1'b0) sel <= 1'b1;

if(sel==1'b1) sel <= 1'b0;

end

end

always @ (*)

begin

case (sel)

8'h00 : outclk_fb <= outclk_0;

8'h01 : outclk_fb <= outclk_1;

endcase

end

assign oe = 1'b1;

assign zdbfbclk = oe ? outclk_fb : 1'bZ;

PLL_DRP_IP PLL_DRP_IP_INST(

.refclk (REFCLK),

.rst (RESET),

.outclk_0 (outclk_0),

.outclk_1 (outclk_1),

.zdbfbclk (zdbfbclk),

.locked (locked)

);

endmodule

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ash_R_Intel,

I tried out your solution and it works in scale down version of my design. Thanks also for sending me the link to cyclone handbook. the explanation is clear about instantiating zdbfbclk port in top entity to mimic and compensate for clk delay from the CLK output port.

But when i put it on a bigger design, it start to fail for:

Error (169026): Pin zdbfbclk with I/O standard assignment 2.5 V is incompatible with I/O bank 3A. I/O standard 2.5 V, has a VCCIO requirement of 2.5V, which incompatible with the I/O bank's VCCIO setting or with other output or bidirectional pins in the I/O bank using a VCCIO requirement of 3.0V. Assign output and bidirectional pins with different VCCIO requirements to different I/O banks, or change the I/O standard assignment for the specified pin to a compatible I/O standard. The Intel FPGA Knowledge Database contains many articles with specific details on how to resolve this error.

Correct me if needed : My interpretation of this error is, the zdbfbclk port need a IO-Standard 2.5V. unfortunately, all the IO-Standard in the bigger design is set to IO-Standard 3.3V and 1.5V. No 2.5V.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You should have if/else in your reset block, not two separate if statements.

You should have a final default clause in your case statement.

I think you're also missing the fbclk input pin that gets enabled in zero-delay buffer mode that's required for the feedback loop for the PLL.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Zero-Delay Bu er mode—the PLL feedback path is confined to the dedicated PLL external output pin. The clock port driven o -chip is phase aligned with the clock input for a minimal delay between the clock input and the external clock output.

Also, Cyclone V Device Handbook: Volume 1: Device Interfaces and Integration (intel.com)

You don't have to generate a feedback clock in your code. Need to simply assign zdbfbclk as an inout port in the top module.

Here is the changed code:

module PLL_DRP(

input REFCLK,

input RESET,

output outclk_0,

output outclk_1,

output reg outclk_fb,

inout zdbfbclk,

output reg sel,

output locked

);

always @ (posedge REFCLK)

begin

if(RESET) sel <= 1'b0;

else

begin

if(sel==1'b0) sel <= 1'b1;

if(sel==1'b1) sel <= 1'b0;

end

end

always @ (*)

begin

case (sel)

8'h00 : outclk_fb <= outclk_0;

8'h01 : outclk_fb <= outclk_1;

endcase

end

assign oe = 1'b1;

//assign zdbfbclk = oe ? outclk_fb : 1'bZ;

PLL_DRP_IP PLL_DRP_IP_INST(

.refclk (REFCLK),

.rst (RESET),

.outclk_0 (outclk_0),

.outclk_1 (outclk_1),

.zdbfbclk (zdbfbclk),

.locked (locked)

);

endmodule

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ash_R_Intel,

I tried out your solution and it works in scale down version of my design. Thanks also for sending me the link to cyclone handbook. the explanation is clear about instantiating zdbfbclk port in top entity to mimic and compensate for clk delay from the CLK output port.

But when i put it on a bigger design, it start to fail for:

Error (169026): Pin zdbfbclk with I/O standard assignment 2.5 V is incompatible with I/O bank 3A. I/O standard 2.5 V, has a VCCIO requirement of 2.5V, which incompatible with the I/O bank's VCCIO setting or with other output or bidirectional pins in the I/O bank using a VCCIO requirement of 3.0V. Assign output and bidirectional pins with different VCCIO requirements to different I/O banks, or change the I/O standard assignment for the specified pin to a compatible I/O standard. The Intel FPGA Knowledge Database contains many articles with specific details on how to resolve this error.

Correct me if needed : My interpretation of this error is, the zdbfbclk port need a IO-Standard 2.5V. unfortunately, all the IO-Standard in the bigger design is set to IO-Standard 3.3V and 1.5V. No 2.5V.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Assign the zdbfbclk to a pin dedicated for PLL feedback. For example Cyclone V has FPLL_[BL,BR,TL,TR]_FB pins dedicated for this functionality. You can find more details in the Pin Connection Guidelines of the device. Probably the bank 3A for your device does not have this pin. Please check pinout files of your device: https://www.intel.com/content/www/us/en/programmable/support/literature/lit-dp.html

Recommend you to let the tool assign the pins in first pass and then you can use it as reference.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ash_R_Intel,

I tried to connect the zdbfbclk port at top entity to the STRATIX V 5SGXA3 series at PIN_AW36(RREF_BL), PIN_AW4(RREF_BR), PIN_B39(RREF_TL) or PIN_B1(RREF_TR), but for some reason, it is giving me Error (171016): Can't place node "zdbfbclk" -- illegal location assignment.

The 2nd alternative i tried was to let the tool assign, and it found a PIN_J16 at bank 7D, which is dedicated for "Other PLL'. But as i compile, it start failing back IO standard 2.5V compatibility issue. After that, i check at the PCBA where the stratix V is placed and found out the bank 7D VCCIO is connected to the 1.5V voltage plane.

unless there is a way to make zdbfbclk port compatible with 1.5V, i don't see a path moving forward.

Many thanks for the advice, learn a lot from this exploration

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Is the requirement mentioned in the handbook fulfilled: "When using this mode, you must use the same I/O standard on the input clocks and clock outputs to guarantee clock alignment at the input and output pins."

Try to assign the input and the zdbfbclk in the same bank and assign same IO standard, in your case 1.5V.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ash,

Per your suggestion, i assigned zdbfbclk to the same bank as the input at bank 3B and since in my stratix V PCBA, this bank is source with 3.0V. I also change the IO standard of zdbfbclk to IO-Standard 3.3-V LVCMOS. And this fix the Error (171016): Can't place node "zdbfbclk" -- illegal location assignment.

Now i am facing another error:

Error (14566): The Fitter cannot place 1 periphery component(s) due to conflicts with existing constraints (1 fractional PLL(s)). Fix the errors described in the submessages, and then rerun the Fitter.

Regards, JJ

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Error (14566): The Fitter cannot place 1 periphery component(s) due to conflicts with existing constraints (1 fractional PLL(s)). Fix the errors described in the submessages, and then rerun the Fitter. The Intel FPGA Knowledge Database may also contain articles with information on how to resolve this periphery placement failure. Review the errors and then visit the Knowledge Database at https://www.altera.com/support/support-resources/knowledge-base/search.html and search for this specific error message number.

Error (175001): The Fitter cannot place 1 fractional PLL, which is within PLL Intel FPGA IP Pll0.

Info (14596): Information about the failing component(s):

Info (175028): The fractional PLL name(s): PLL_DRP:PLL_DRP_INST|Pll0:PLL_MAIN_INST|Pll0_0002:pll0_inst|altera_pll:altera_pll_i|altera_stratixv_pll:stratixv_pll|altera_stratixv_pll_base:fpll_0|fpll

Error (16234): No legal location could be found out of 12 considered location(s). Reasons why each location could not be used are summarized below:

Error (175006): Could not find path between source pin and the fractional PLL

Info (175026): Source: pin zdbfbclk

Info (175015): The I/O pad zdbfbclk is constrained to the location PIN_AC28 due to: User Location Constraints (PIN_AC28)

Info (14709): The constrained I/O pad is contained within this pin

Info (175021): The pin was placed in location AC28

Error (175022): The fractional PLL could not be placed in any location to satisfy its connectivity requirements

Info (175029): 12 locations affected

Info (175029): FRACTIONALPLL_X0_Y1_N0

Info (175029): FRACTIONALPLL_X0_Y10_N0

Info (175029): FRACTIONALPLL_X0_Y91_N0

Info (175029): FRACTIONALPLL_X0_Y100_N0

Info (175029): FRACTIONALPLL_X92_Y2_N0

Info (175029): FRACTIONALPLL_X92_Y11_N0

Info (175029): FRACTIONALPLL_X92_Y87_N0

Info (175029): FRACTIONALPLL_X92_Y96_N0

Info (175029): FRACTIONALPLL_X202_Y1_N0

Info (175029): FRACTIONALPLL_X202_Y10_N0

Info (175029): FRACTIONALPLL_X202_Y91_N0

Info (175029): FRACTIONALPLL_X202_Y100_N0

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry for the late response. Can you please cross check the pinout files of your target device, whether the allocated pin AC28 is a FPLL_*_FB pin?

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ash_R_Intel,

Good to hear from you.

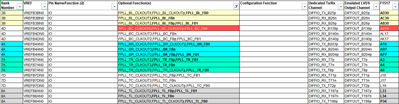

I finally understand your emphasis on FPLL_*_FB. I cross check with the 5SGXA3 series pinout file and AC28 is not one of them. The pins for FPLL_*_FB in STRATIX V are :

I free up the pins in above map in the stratix V and zdbfbclk is now map to AH16 (in bank 4D) which is FPLL_BC_FB0. And the compilation is successful.

Many thanks, learn a lot from you, JJ

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page