- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Getting this hold timing error. Need help resolving it.

PLL cross checking found inconsistent PLL clock settings:

Clock: i_DAC_TOP|i_PLL|pll_inst|altera_pll_i|general[0].gpll~FRACTIONAL_PLL|vcoph[0] with master clock period: 40.000 found on PLL node: i_DAC_TOP|i_PLL|pll_inst|altera_pll_i|general[0].gpll~FRACTIONAL_PLL|vcoph[0] does not match the master clock period requirement: 0.040

Any help is greatly appreciated.

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

No, you didn't have to break out the PLL output clocks like that. derive_pll_clocks is fine. I was referring to the 3 extra create_clock statements you have (sclk, clk_divider...). Those are coming from internal registers, not an input port of the device, so they should be in your .sdc as create_generated_clock commands, not create_clock.

As for the failing paths, those look like they are going to Signal Tap, which is debug logic that will be eventually removed. You don't really need to meet timing there.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

"master clock period requirement: 0.040" sounds like a .sdc typo. Show the respective constraint.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello FvM,

I am a little new to this and so the thing is that I am not able to understand which clock is causing this error. The PLL is used to create four clocks:

Reference clock frequency is 25Mhz and Operation Mode is "Direct".

outclk0: 100Mhz

outclk1: 20Mhz

outclk2: 1.63Mhz

outclk3: 150Mhz

I am using a DE10 Standard FPGA which has Cyclone V SoC.

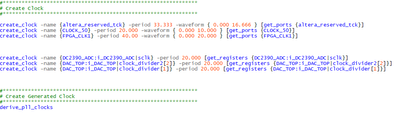

I have attached a screenshot of the sdc file below.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You may find this thread useful: https://community.intel.com/t5/Programmable-Devices/How-to-deal-with-this-warning/td-p/76741

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Nurina,

I checked the Megawizard options. It doesn't have a "no compensation" mode. I am currently working on a DE10 Standard FPGA with Cyclone V SoC.

Below is the attached screenshot:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

FYI, you can't use create_clock to create internal clocks like that. You need to use create_generated_clock. I don't think that's related to the issue, though.

Is FPGA_CLK1 the input clock reference for the PLL? I presume it is based on the frequency, but the error is indicating that the wrong clock is being used as the reference input for the PLL.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sstrell,

FPGA_CLK1 clock is input to altcltctrl ip, then the output of altclkctrl is used in the PLL as the reference clock.

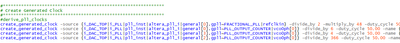

Would you still suggest to use create_generated_clock for FPGA_CLK1? I updated my sdc with these 4 lines using the derive_pll_clocks, let me know if this is correct:

1) create_generated_clock -source {i_DAC_TOP|i_PLL|pll_inst|altera_pll_i|general[0].gpll~FRACTIONAL_PLL|refclkin} -divide_by 2 -multiply_by 48 -duty_cycle 50.00 -name {i_DAC_TOP|i_PLL|pll_inst|altera_pll_i|general[0].gpll~FRACTIONAL_PLL|vcoph[0]} {i_DAC_TOP|i_PLL|pll_inst|altera_pll_i|general[0].gpll~FRACTIONAL_PLL|vcoph[0]}

2) create_generated_clock -source {i_DAC_TOP|i_PLL|pll_inst|altera_pll_i|general[0].gpll~PLL_OUTPUT_COUNTER|vco0ph[0]} -divide_by 6 -duty_cycle 50.00 -name {i_DAC_TOP|i_PLL|pll_inst|altera_pll_i|general[0].gpll~PLL_OUTPUT_COUNTER|divclk} {i_DAC_TOP|i_PLL|pll_inst|altera_pll_i|general[0].gpll~PLL_OUTPUT_COUNTER|divclk}

3) create_generated_clock -source {i_DAC_TOP|i_PLL|pll_inst|altera_pll_i|general[3].gpll~PLL_OUTPUT_COUNTER|vco0ph[0]} -divide_by 4 -duty_cycle 50.00 -name {i_DAC_TOP|i_PLL|pll_inst|altera_pll_i|general[3].gpll~PLL_OUTPUT_COUNTER|divclk} {i_DAC_TOP|i_PLL|pll_inst|altera_pll_i|general[3].gpll~PLL_OUTPUT_COUNTER|divclk}

4) create_generated_clock -source {i_DAC_TOP|i_PLL|pll_inst|altera_pll_i|general[2].gpll~PLL_OUTPUT_COUNTER|vco0ph[0]} -divide_by 366 -duty_cycle 50.00 -name {i_DAC_TOP|i_PLL|pll_inst|altera_pll_i|general[2].gpll~PLL_OUTPUT_COUNTER|divclk} {i_DAC_TOP|i_PLL|pll_inst|altera_pll_i|general[2].gpll~PLL_OUTPUT_COUNTER|divclk}

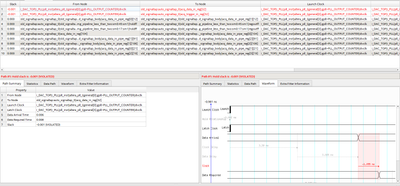

Also, here's the timing analyzer screenshot to give you some more information on the error:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

No, you didn't have to break out the PLL output clocks like that. derive_pll_clocks is fine. I was referring to the 3 extra create_clock statements you have (sclk, clk_divider...). Those are coming from internal registers, not an input port of the device, so they should be in your .sdc as create_generated_clock commands, not create_clock.

As for the failing paths, those look like they are going to Signal Tap, which is debug logic that will be eventually removed. You don't really need to meet timing there.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Excellent! That is extremely helpful! Thank you!

As for the create_generated_clock command, could you point out to an article or suggest me how to get the template for them? How do I get their source (sclk,clock_divider2 etc.)?

Thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The source is whatever clock or input pin that is driving the register or logic that produces the new clock. Think of it like a chain of cascading clocks. create_clock is only used for the start of the chain. Everything else is generated based on a previous clock.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello sstrell,

Got it! This is excellent! Thank you so much for the help! I really appreciate it!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, Feel free to open a new thread or login to ‘ https://supporttickets.intel.com ’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

If any answer from the community or Intel Support are helpful, feel free to rank your support experience by rating 4/5 survey. Please let me know of any inconvenience so that I may improve your future service experience.

Best regards,

Nurina

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page