- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

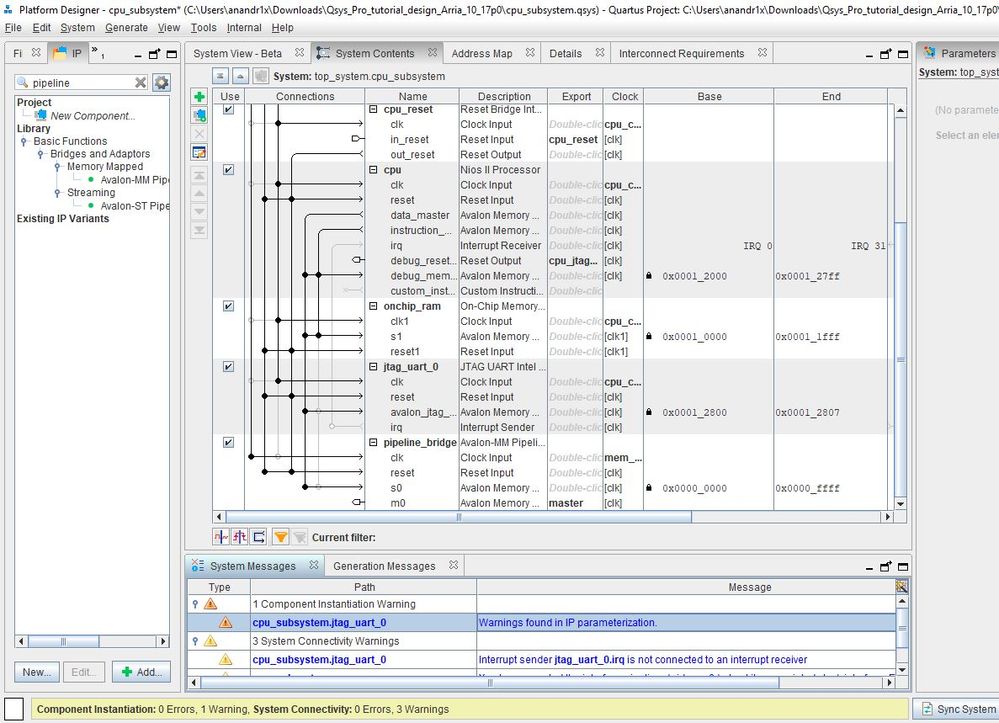

I am following the guide AN 812: Platform Designer System Design Tutorial, I received the below error.

Error: sysA.cpu.data_master: pipeline_bridge.s0 (0x0..0xffff) is outside the master's address range (0x0..0xfff)How to solve this structurally? (Using Platform Designer 18.1 Build 222)

Link Copied

3 Replies

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes,i can reproduce the error.However we can solve it

Before assign the Base address and click on lock, we have go to do system ->assign Base address.and assign the Base address and click on lock as per AN812.

Let me know if this has helped resolve the issue you are facing or if you need any further assistance.

Best Regards,

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The problem is solved.

Reply

Topic Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page