- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there,

I want to convert a huge project which contains around 45 sub modules and around 44 ip cores of xilinx from Xilinx to intel, Is there any way to convert else i have to do it from the scratch level.

How to define a parameter outside the module of a HDL Code in altera, Please share me the format for defining a keyword parameter in HDL Code.

Thanks in Advance

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I believe I have provided the support/answer that you needed in order to proceed with your project. With that, this thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

Best Regards,

Richard Tan

p/s: If any answer from the community or Intel support are helpful, please feel free to give Kudos.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We have an internal tool that will help to convert the design using UltraScale and UltraScale+ to our Agilex device.

There is limitations for other Xilinx devices: example some primitives are not supported.

Also, the Xilinx project files will not added to the Intel project:

- The Xilinx Vivado generated files (including IPs, Xilinx templates, or any other files that are under Xilinx license)

- The constraints

- Block Design files

Plus you have 44 ip cores of Xilinx, all of it will be black box.

If you want me to convert the design, you will need to provide me the .xpr project files. Once converted, I will send you back the .qpf files and you can start work on your design.

To define a parameter outside the module of a HDL, the Quartus software allows you to assign global, project-wide default values for parameters on the Default Parameter Settings page in the Settings dialog box. You may checkout this.

https://www.doulos.com/knowhow/fpga/settings-genericsparameters-for-synthesis/

Best Regards,

Richard Tan

p/s: If any answer from the community or Intel support are helpful, please feel free to give Kudos.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Richard Tan,

Thanks for saying that you will be converting the modules if i share u the xpr file, Is it possible to convert the complete project from xpr to qpf and can expect that it will work fine

May I compress the complete xilinx project with required support files and can i share it to you, Will u able to convert it

With Regards,

V.Mathiazhagan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Mathiazhagan

If your design contain purely RTL, there is a possibility that it will work fine but since your design contain Xilinx IP core, I have my doubt there. It may need some work after converting the design, e.g. replacing the xilinx MMCM to intel PLL.

You may checkout this document.

If the compressed xilinx project can be fully compiled again in Vivado, I think it should be good to go.

Best Regards,

Richard Tan

p/s: If any answer from the community or Intel support are helpful, please feel free to give Kudos.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Richard Tan,

I will be sharing you the entire project as a ZIP File where you can extract and run it on a vivdo software that to be converted into intel quartus Project, I should be really very much thankful to you if u can convert the entire project into an Quartus project.

The total size of the project is 378MB, Shall i upload it on a drive and share u the link of the drive from where it can be downloaded , will u be able to download it from the drive link

With Regards,

V.Mathiazhagan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Richard Tan,

I have attached the link of the project files from where it can be downloaded, kindly go through and do the needful, awaiting for your favorable response

https://drive.google.com/file/d/1c3pyTHEksl6s5GxOEc--xXOAeS6CQS8z/view?usp=sharing

With Regards,

V.Mathiazhagan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Mathiazhagan

It seems the drive need an account to access it. I am reluctant to access it through my personal account. Does it accessible without an account needed?

If you do not wish to share the design publicly, you can share it through FTP (filezilla) platform and I will send you an email with the details. You may drop the file there.

Best Regards,

Richard Tan

p/s: If any answer from the community or Intel support are helpful, please feel free to give Kudos.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Richard Tan,

I have received the mail i will be sharing the files via filezilla, Kindly do the needful

With Regards,

V.Mathiazhagan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

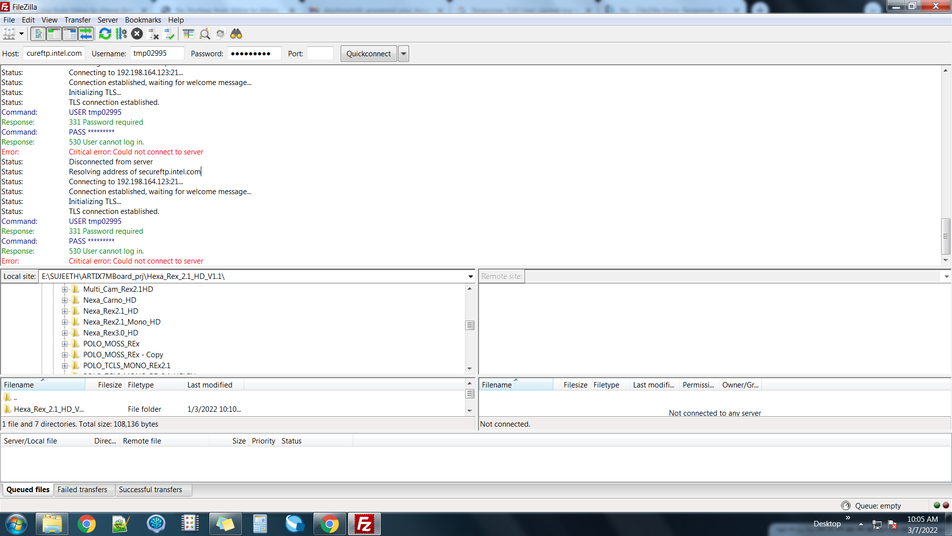

Dear Richard Tan,

Am getting a error

Response: 530 User cannot log in.

Error: Critical error: Could not connect to server

Kindly help me out how to resolve this issue

With Regards,

V.Mathiazhagan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

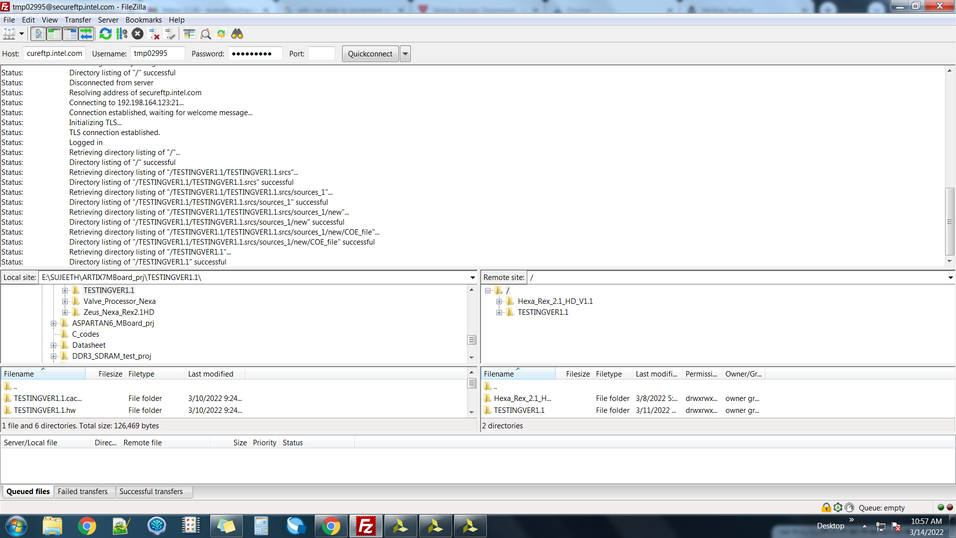

I can see the folder Hexa_Rex_2.1_HD_V1.1 in the directory. Is this the folder with the xpr project?

Are you still having connection problem with ftp?

Regards,

Richard Tan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Richard Tan,

No i don't have any problem with the ftp, The folder Named Hexa_Rex_2.1_HD_V1.1 in the directory is the folder which contains the xpr project, Kindly go through it and do the needful.

With Regards,

V.Mathiazhagan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

When I try to convert the project, the tool error out that below file is missing. Please kindly check and ensure that the files is provided.

../Hexa_Rex_2.1_HD_V1.1/Hexa_Rex_2.1_HD_V1.1.srcs/sources_1/new/HD_SORTER/calib_Bram_IF.v doesn't exist in the Xilinx project directory.

Try to compile the design with the attachment that you provided. If it can't, probably means there is something wrong.

Best Regards,

Richard Tan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Richard Tan,

Sorry for that happened, Actually it is a compiled file don't know what is the issue happened, I Will be once again sharing you the project files via ftp.

With Regards,

V.Mathiazhagan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Richard Tan,

I have once again shared you the project files via ftp. Kindly look into it and let me know if you have any issues regarding the file shared. The file shared is the compiled one, Which is synthesized at my end in vivado 2015.4 version without any runtime error.

With Regards,

V.Mathiazhagan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Richard Tan,

I have shared the files via file zilla using the credentials shared by you, Kindly let me know whether you received the files, Just to know an acknowledgement whether the files received on your side successfully.

With Regards,

V.Mathiazhagan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Richard Tan,

Have u went through the files which i have shared, Kindly let me know am awaiting for your favorable response

With Regards,

V.Mathiazhagan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Mathiazhagan,

I have attached the intel_project.zip in the ftp.

Please remind that the tool could only convert the design to Agilex device which is in Quartus Pro. If you plan to use in other Quartus version, you may try to open a new project and add the respective files.

Also Device xc7a35tftg256-1 is not supported. Some primitives/macros may not detected during the conversion.

You will need to check the x2i_primitive_lib.sv file to know which primitive has been blackbox and you will need replace it with an equivalent primitive.

Same goes to the IPs. You will need to instantiate the equivalent intel IPs. e.g. IOPLL, adder,

Best Regards,

Richard Tan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Richard Tan,

Am not able to view the intel_project.zip file in the ftp, could u please upload it once again.

With Regards,

V.Mathiazhagan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear RichardTanSY

Am not able to view the zip file shared by you,

I have attached the screen shot of the filezilla for your kind reference

With Regards,

V.Mathiazhagan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have re-attached the intel_project.zip. Please kindly check again.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear RichardTanSY,

Thanks a lot for converting i don't have the quartus prime pro edition, I have only standard edition of 18.1 how to add the project file by creating new project, The qpf file is not getting added to my project, so will you be able to assist me in this how to do.

With Regards,

V.Mathiazhagan

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page