- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have attached a qar file that was archived with Quartus 18.0. When we restored this project and compiled, we got a different RBF file than the original SRM_VENTNOR.rbf file that is attached. Each time we compiled we would get a different RBF file (undesirable). I suspect there is a setting or file that is forcing the tool to generate a new rbf file for each compile. Could you please review qar file and investigate root cause?

Please note that the SRM_VENTNOR.rbf file is archived in the SRM_VENTNOR.zip file.

Thanks,

Phil

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

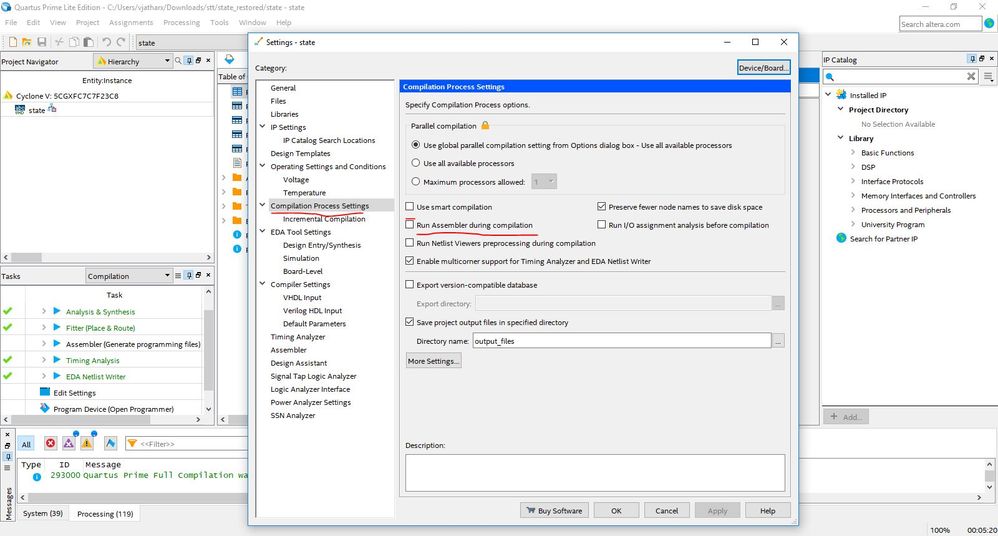

How is the .rbf file different? Any time the Assembler runs during a full compilation, it will generate a new programming file. You can choose to not run the Assembler automatically during a full compilation in the compiler settings.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I diffed the two .rbf files with the tool KDiff3 and they were not binary equivalents. I have two other FPGA projects compiled with Quartus 18.0 multiple times and the output .rbf files were always identical. What is the function of the Assembler?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Assembler generates programming & configuration files in Quartus tool.

whenever you compile the design in Quartus tool, the assembler automatically generates the programming files. It also allows to convert configuration files to programming files for configuration devices.

Have to checked the previous post about Assembler(uncheck) option during compilation?

Refer the screenshot & try to compare again.

Assignments -> Settings..

please let me know, how it woks for you.

Regards,

Vicky

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the reply. I understand that the Assembler generates all the programming files and can be turned off during compilation, but that does not address my original concern where the output of the compilation (RBF file) is different for each iteration. We should get the exact same output every time we compile since the input source files and compile settings are the same. Could you please review that attached QAR file and investigate what is the root cause for this issue? Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Apologies for the late response.

I tried to compare(Using Non Intel KDiff3 Tool, which we can`t give surety) the .rbf files generated from project provided in very first post & I observed that, there is conflict. I also realized the same behavior for two different projects which consist of one or more IPs used in design but, when I tried to compare .rbf file generated after multiple time of compilation of a project(which doesn`t consist of IP/IPs in design), got result identical .rbf files so I am not sure the exact reason but observation is that the design which consists of IPs differs while compilation.

Regards,

Vicky

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Vicky,

I have a similar FPGA design that varies from the project from the very first post just slightly. This similar design uses many of the same IPs but it compares with NO differences after each compile. Please investigate further what the root cause is for this issue. The tool should generate the exact same output for every compile since the input source files and compile settings are the same.

Thanks,

Phil

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Could you provide that similar FPGA design for comparison purpose?

check another design which should have IPs but excluding PLL, you can also check with different edition & version of Quartus

Thanks,

Vicky

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I've uploaded the similar FPGA design (SRM_5000.qar) along with the output RBF file (SRM_5000.rbf). You will need to extract the SRM_5000.rbf file from the SRM_5000_RBF zip file.

Please restore this design and compile twice. A comparison of the two output RBF files will show that they are binary equivalents. Please investigate root cause of this issue. Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I attached it again. Please confirm you can download the SRM_5000.qar file.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for the design.

I checked with your design & observed that .rbf files generated from this project shows equivalent by KDiff3 Tool even this project consists of PLL IP. so as you mentioned in your very first post , there might be some issue with that design.

let me check with my team since issue is replicated & get back to you.

Regards,

Vicky

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please double check the compiler settings between the two QAR files as well to ensure that it's not any compiler setting causing the issue. Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Vicky,

I am the Intel PSG FAE at Arrow that supports this customer and I could replicate the issue also but could not explain why this issue was happening. I looked at the "good" design to check the settings and didn't see anything different from the "bad" design.

Have you or your team had a chance to investigate why this one design from the customer gets different RBF files after each compile?

Steve Zack

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi PFong2 & SZack,

Could you please check again by creating the fresh deign with all the files included in that erroneous design?

we are working on it & will let you know once we get any update.

Thanks,

Vicky

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Vicky,

We have two designs that use the similar core modules that do not exhibit this issue. Only the initial design (SRM_VENTNOR) that I sent you has this issue. It's been over two months since I submitted this inquiry. Could we escalate this issue so we can converge on a resolution sooner than later?

Thanks,

Phil

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Phil,

This case got escalated to me at this point. I will contact you via email for further clarifications.

Thanks,

Joseph

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Phil,

Please contact your distributor as we've got internal ticket resolved for this. They will provide further clarification in details.

Thanks,

Joseph

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page