- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi guys,

I have little example code:

A generic package:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

package test_pkg is

generic(

N : positive := 20

);

type t_arr is array(natural range <>) of std_logic_vector(N-1 downto 0);

type t_rec is record

data : t_arr(0 to 3);

end record;

end test_pkg;

package body test_pkg is

end test_pkg;A instance of the generic package:

library ieee;

package test10_pkg is new work.test_pkg

generic map (

N => 10

);And a rtl-testbench:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

use work.test10_pkg.all;

entity tb is

port(

test1_in : in t_rec;

test1_out1 : out t_rec;

test1_out2 : out t_arr(0 to 3);

test1_out3 : out std_logic_vector(9 downto 0);

test1_out4 : out std_logic;

test1_out5 : out std_logic_vector(1 downto 0)

);

end tb;

architecture rtl of tb is

begin

test1_out1 <= test1_in;

test1_out2 <= test1_in.data;

test1_out3 <= test1_in.data(0);

test1_out4 <= test1_in.data(1)(5);

test1_out5 <= test1_in.data(1)(3 downto 2);

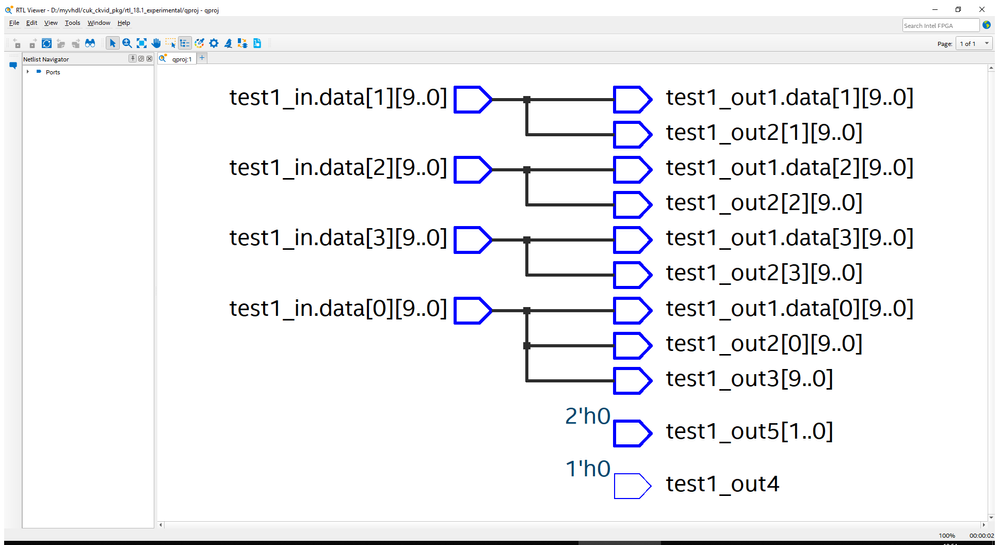

end rtl;And a screenshot of the RTL:

Can some explain why the outputs 4 and 5 are not connected in the RTL?

Best Regards

Oliver

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am using Prime Pro 18.1.2 Build 277.

I am surprised because the IEEE 1076-2008 fixpoint package is a generic package. Surely you must have support for that.

Regards

Oliver

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

sorry I cannot open the file in 18.2 - I do not have a 19.2 installation.

I have checked again in 18.2, my code example compiles fine. Just copy the three parts as they are, e.g. in a single file called tb.vhd, make it the top-level, set vhdl-2008 option and off you go.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have tested the example code above with modelsim and it works just fine. The version I used is this:

> ModelSim - INTEL FPGA STARTER EDITION 10.6d

> Revision: 2018.02

> Date: Feb 24 2018

Can you comment any further on the issue why this happens?

Regards

Oliver

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I try to run the simulation, it shows that test1-out5 and test1_4 is having zero value. Which is the code that you had written is not recognized in modelsim as well.

If you can prove the code in IEEE std should be usable, I can help to file an enhancement for you. Will attached for you on this.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

In you screenshot, you clearly see that modelsim does recognize it because it changes from "red" (X) to "0". And second, your stimulus is wrong, please try again with the following:

force -freeze sim:/tb/test1_in.data(0) 10'hFFF 0

The bits (5) and (3 downto 2) are used, with h"111" you just stimulated bit (0),(4) and (8).

thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please try all of the arrays elements, as you did before!

force -freeze sim:/tb/test1_in.data(0) 10'hFFF 0

force -freeze sim:/tb/test1_in.data(1) 10'hFFF 0

force -freeze sim:/tb/test1_in.data(2) 10'hFFF 0

force -freeze sim:/tb/test1_in.data(3) 10'hFFF 0

thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page