- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

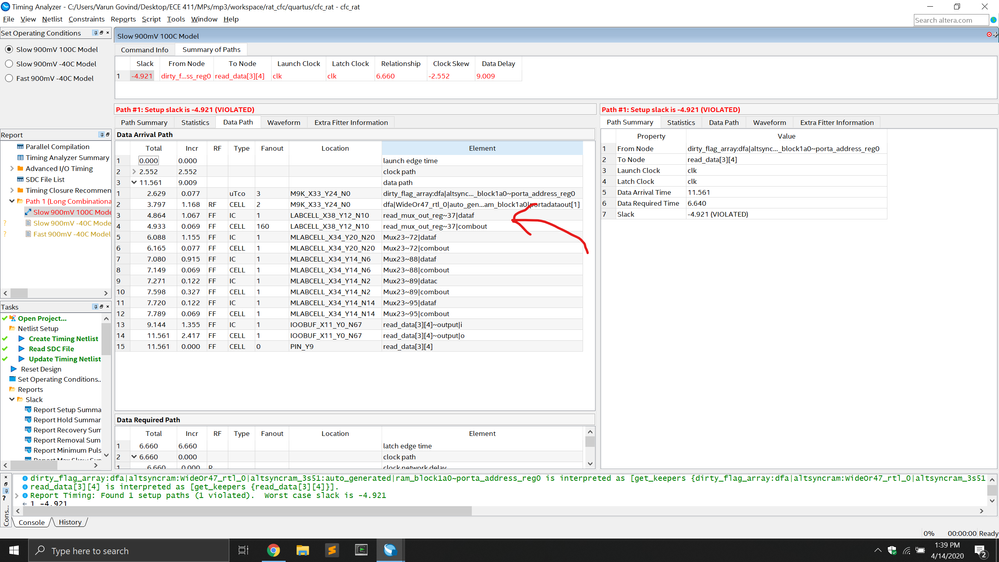

I'm trying to optimize a part of my design to meet my timing goal (150 MHz ~6.66ns path) but one register is not being read as a register on my timing analysis and I don't know why. In the timing analyzer it shows the register cell as a logical cell in the middle of the path, however, since it is a register, it should be at the end of the path.

My design has 2-stages (i.e. pipelined), at least it is supposed to be but the analyzer is not reading the variable as a register.

Here is the code snippet in question:

always_ff @(posedge clk) begin

if (rst) begin

for (int i = 0; i < 6; i++)

read_mux_out_reg[i] <= 0;

end

else begin

for (int i = 0; i < 6; i++)

read_mux_out_reg[i] <= read_mux_out[i];

end

endHere is the critical path shown in timing analyzer:

Is there something I need to be doing in the timing analyzer for this to work? Any help is greatly appreciated, I've been stuck on this for a while and I've tried a bunch of things to synthesize a register but none of the I tried change the result of the timing analyzer.

Thank you~

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Well, I figured out my problem. It is because there was a lot of mux concatenation from my arrays to the output (This is because I read combinationaly). I simply added another pipeline stage to compensate and now I am meeting my timing requirements.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page