- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

I'm trying to translate to Verilog some Maxplus2 examples (in .bdf format) of TTL gates but I get some errors when compiling.I'm using Quartus 12.1

For example, this is the generated Verilog from the 7474.bdf file :

/ Copyright (C) 1991-2012 Altera Corporation

// Your use of Altera Corporation's design tools, logic functions

// and other software and tools, and its AMPP partner logic

// functions, and any output files from any of the foregoing

// (including device programming or simulation files), and any

// associated documentation or information are expressly subject

// to the terms and conditions of the Altera Program License

// Subscription Agreement, Altera MegaCore Function License

// Agreement, or other applicable license agreement, including,

// without limitation, that your use is for the sole purpose of

// programming logic devices manufactured by Altera and sold by

// Altera or its authorized distributors. Please refer to the

// applicable agreement for further details.

// PROGRAM "Quartus II 64-Bit"

// VERSION "Version 12.1 Build 177 11/07/2012 SJ Web Edition"

// CREATED "Thu Apr 09 22:15:40 2020"

module \7474 (

2CLRN,

2CLK,

2D,

2PRN,

1CLRN,

1CLK,

1D,

1PRN,

1Q,

1QN,

2Q,

2QN

);

input wire 2CLRN;

input wire 2CLK;

input wire 2D;

input wire 2PRN;

input wire 1CLRN;

input wire 1CLK;

input wire 1D;

input wire 1PRN;

output wire 1Q;

output wire 1QN;

output wire 2Q;

output wire 2QN;

reg DFF_10;

reg DFF_9;

assign 1Q = DFF_9;

assign 2Q = DFF_10;

always@(posedge 2CLK or negedge 2CLRN or negedge 2PRN)

begin

if (!2CLRN)

begin

DFF_10 <= 0;

end

else

if (!2PRN)

begin

DFF_10 <= 1;

end

else

begin

DFF_10 <= 2D;

end

end

assign 2QN = ~DFF_10;

assign 1QN = ~DFF_9;

always@(posedge 1CLK or negedge 1CLRN or negedge 1PRN)

begin

if (!1CLRN)

begin

DFF_9 <= 0;

end

else

if (!1PRN)

begin

DFF_9 <= 1;

end

else

begin

DFF_9 <= 1D;

end

end

endmodule

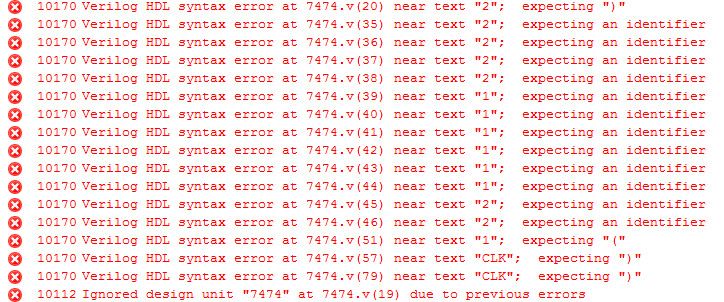

When I try to compile it I get the errors in the attached snapshot.I'm able to compile Verilog code generated from most of the .bdf examples (like 74157.bdf).Any ideas why I get errors when compiling Verilog code generated from this 7474.bdf Maxplus2 example ?Thanks in advance.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Port and signal names cannot start with a digit. The name must be escaped when used (ie, change 2CLK to \2CLK AND add a trailing space after the name).

So for example 'input wire 2CLRN;' becomes 'input wire \2CLRN ;' etc.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

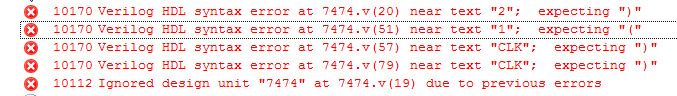

Thanks for reply.I changed the syntax in this way and I got less errors (snapshot attached)

// Copyright (C) 1991-2012 Altera Corporation

// Your use of Altera Corporation's design tools, logic functions

// and other software and tools, and its AMPP partner logic

// functions, and any output files from any of the foregoing

// (including device programming or simulation files), and any

// associated documentation or information are expressly subject

// to the terms and conditions of the Altera Program License

// Subscription Agreement, Altera MegaCore Function License

// Agreement, or other applicable license agreement, including,

// without limitation, that your use is for the sole purpose of

// programming logic devices manufactured by Altera and sold by

// Altera or its authorized distributors. Please refer to the

// applicable agreement for further details.

// PROGRAM "Quartus II 64-Bit"

// VERSION "Version 12.1 Build 177 11/07/2012 SJ Web Edition"

// CREATED "Fri Apr 10 21:19:39 2020"

module \7474 (

2CLRN,

2CLK,

2D,

2PRN,

1CLRN,

1CLK,

1D,

1PRN,

1Q,

1QN,

2Q,

2QN

);

input wire \2CLRN ;

input wire \2CLK ;

input wire \2D ;

input wire \2PRN ;

input wire \1CLRN ;

input wire \1CLK ;

input wire \1D ;

input wire \1PRN ;

output wire \1Q ;

output wire \1QN ;

output wire \2Q ;

output wire \2QN ;

reg DFF_10;

reg DFF_9;

assign 1Q = DFF_9;

assign 2Q = DFF_10;

always@(posedge 2CLK or negedge 2CLRN or negedge 2PRN)

begin

if (!2CLRN)

begin

DFF_10 <= 0;

end

else

if (!2PRN)

begin

DFF_10 <= 1;

end

else

begin

DFF_10 <= 2D;

end

end

assign 2QN = ~DFF_10;

assign 1QN = ~DFF_9;

always@(posedge 1CLK or negedge 1CLRN or negedge 1PRN)

begin

if (!1CLRN)

begin

DFF_9 <= 0;

end

else

if (!1PRN)

begin

DFF_9 <= 1;

end

else

begin

DFF_9 <= 1D;

end

end

endmodule

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok, maybe I was not being clear enough. ANYWHERE a non-standard format identifier (ie, starting with an alphabetic, and then containing only alphabetic, numeric, or underscore) is used it MUST be escaped. So in your above code, the identifiers in the module port list, in the assign statements, and those in equations in the always blocks need escaping. Here is what your code should look like:

module \7474 (

\2CLRN ,

\2CLK ,

\2D ,

\2PRN ,

\1CLRN ,

\1CLK ,

\1D ,

\1PRN ,

\1Q ,

\1QN ,

\2Q ,

\2QN

);

input wire \2CLRN ;

input wire \2CLK ;

input wire \2D ;

input wire \2PRN ;

input wire \1CLRN ;

input wire \1CLK ;

input wire \1D ;

input wire \1PRN ;

output wire \1Q ;

output wire \1QN ;

output wire \2Q ;

output wire \2QN ;

reg DFF_10;

reg DFF_9;

assign \1Q = DFF_9;

assign \2Q = DFF_10;

always @(posedge \2CLK or negedge \2CLRN or negedge \2PRN )

begin

if (!\2CLRN )

begin

DFF_10 <= 0;

end

else

if (!\2PRN )

begin

DFF_10 <= 1;

end

else

begin

DFF_10 <= \2D ;

end

end

assign \2QN = ~DFF_10;

assign \1QN = ~DFF_9;

always@(posedge \1CLK or negedge \1CLRN or negedge \1PRN )

begin

if (!\1CLRN )

begin

DFF_9 <= 0;

end

else

if (!\1PRN )

begin

DFF_9 <= 1;

end

else

begin

DFF_9 <= \1D ;

end

end

endmodule

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Caius,

According to your Verilog code, you are using first character for your identifier in module,port,signal assignment and statement equation with number. Either you change to new name for identifier or put ("\") if you want to keep the identifier naming. This is a escaped identifier as it allow for any printable ASCII character to be included in the name. Escaped identifiers begin with white space. The backslash (“\”) character leads off the identifier, which is then terminated with white space. The leading backslash character is not considered part of the identifier.

Thus in your program,

module \7474 (

\2CLRN ,

\2CLK ,

\2D , /* port identifer declaration put "\" */

\2PRN ,

\1CLRN ,

\1CLK ,

\1D ,

\1PRN ,

\1Q ,

\1QN ,

\2Q ,

\2QN

);

input wire \2CLRN ;

input wire \2CLK ;

input wire \2D ;

input wire \2PRN ;

input wire \1CLRN ; /* signal assingment put "\" */

input wire \1CLK ;

input wire \1D ;

input wire \1PRN ;

output wire \1Q ;

output wire \1QN ;

output wire \2Q ;

output wire \2QN ;

reg DFF_10;

reg DFF_9;

assign \1Q = DFF_9;

assign \2Q = DFF_10;

always @(posedge \2CLK or negedge \2CLRN or negedge \2PRN )

begin

if (!\2CLRN )

begin

DFF_10 <= 0;

end

else

if (!\2PRN )

begin

DFF_10 <= 1;

end

else

begin

DFF_10 <= \2D ; /* statement all identifier put "\" */

end

end

assign \2QN = ~DFF_10;

assign \1QN = ~DFF_9;

always@(posedge \1CLK or negedge \1CLRN or negedge \1PRN )

begin

if (!\1CLRN )

begin

DFF_9 <= 0;

end

else

if (!\1PRN )

begin

DFF_9 <= 1;

end

else

begin

DFF_9 <= \1D ;

end

end

endmodule

Thanks,

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Many thanks for suggestions and help, I'm now able to successfully compile.Last thing : is there a way to convert schematics drawn with EDA softwares (ike Kicad) to Verilog compatible with Quartus?I could draw schematics block in Quartus and then convert to Verilog but it's a pain.Thanks in advance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

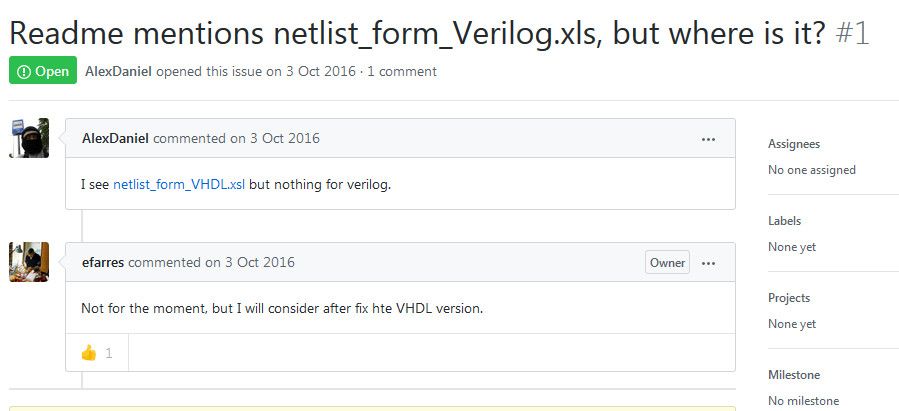

You miight try this: https://github.com/efarres/KiCad-HDL

It has several netlist translator plugins for KiCad that can translate the intermediate XLST format to various other formats (verilog and vhdl in particular).

I have not used this translation tool in particular (but I do use KiCAD for PCB schematics). The generated verilog should be pretty vanilla format.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for reply.I tried in the past this plugin and found that the Verilog translation is not yet implemented, only VHDL is supported although still bugged according to the author.I attach a snapshot of what he said about.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Caius,

You can actually use Quartus to do that, conversion from schematic to HDL (Verilog/VHDL).

Thanks,

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, I know.The problems is that I have all my schematics done in Kicad (some are very big) and translating them to Quartus would be a huge job also because the schematics entry in Quartus is not really user-friendly and intuitive.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page