- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

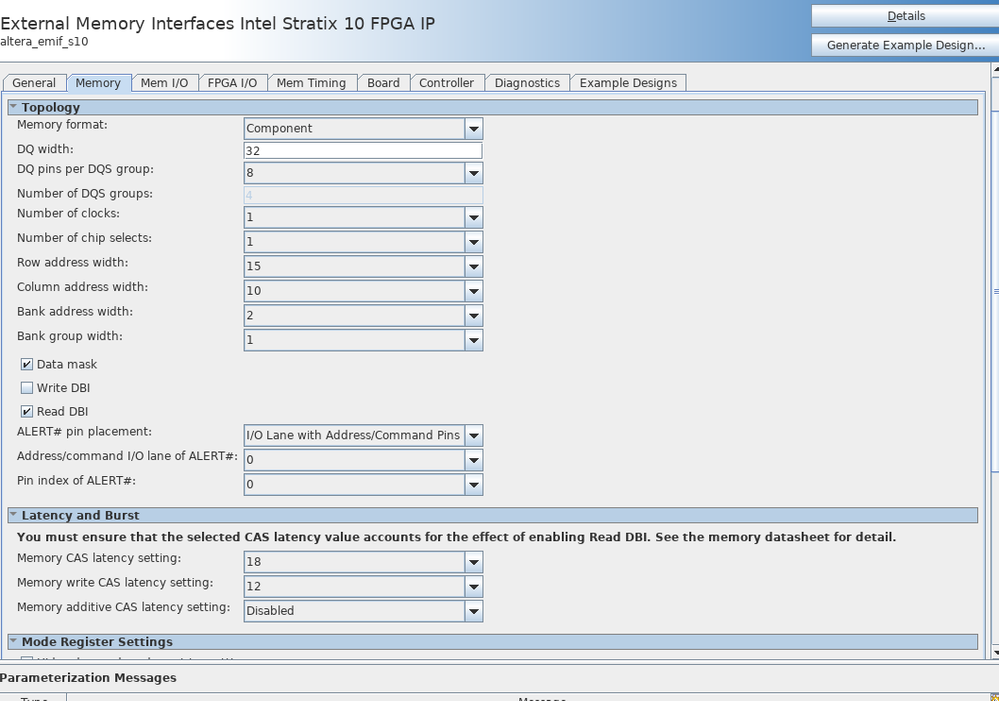

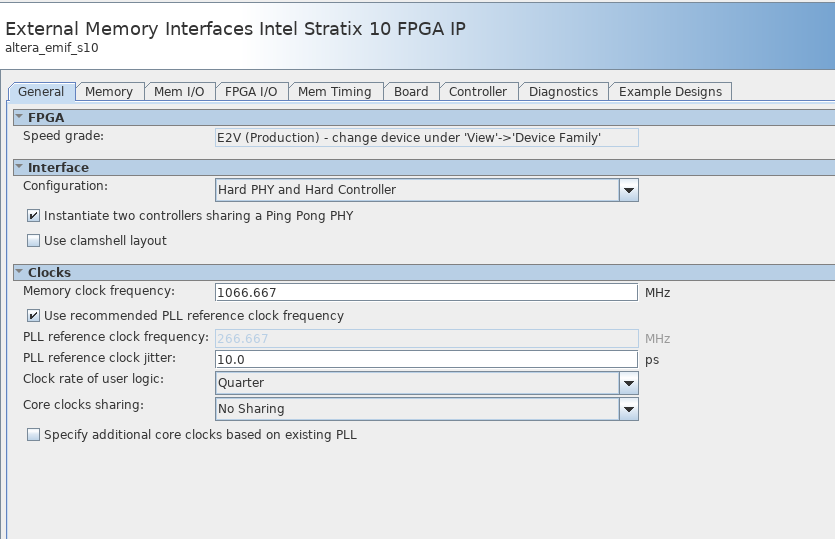

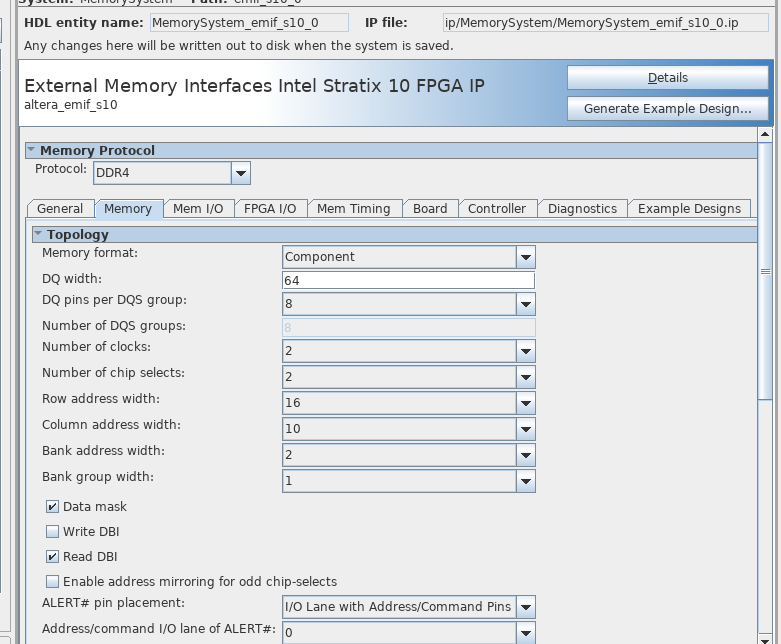

My EMIF is set to ping-pong PHY, because the device contains two teams of CK, CKE, cs_n, ODT, but in the plan stage, such errors are always reported:

Error(18612): READDATAVALID signal for secondary memory controller's Avalon Memory Mapped bus is not connected for memory interface IP "MemorySystem_emif_s10_0". Connect this port to an FPGA core signal.

Error(15307): Cannot apply project assignments to the design due to illegal or conflicting assignments. Refer to the other messages for corrective action.

I just understand what's wrong with READDATAVALID. here is my EMIF parameter select :

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

others are default.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The error message description doesn't complain about EMIF Ping Pong PHY setting but rather more on the EMIF interface avalon connection issue.

Can you check back your Platform designer (or previously QSYS) design on the EMIF IP avalon port connection ?

make sure you export it to QSYS top level file as "conduit"

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

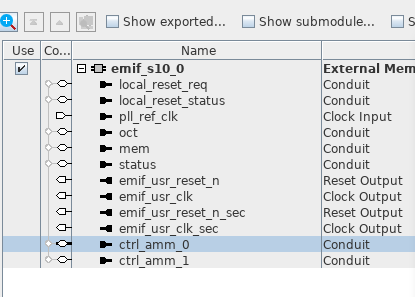

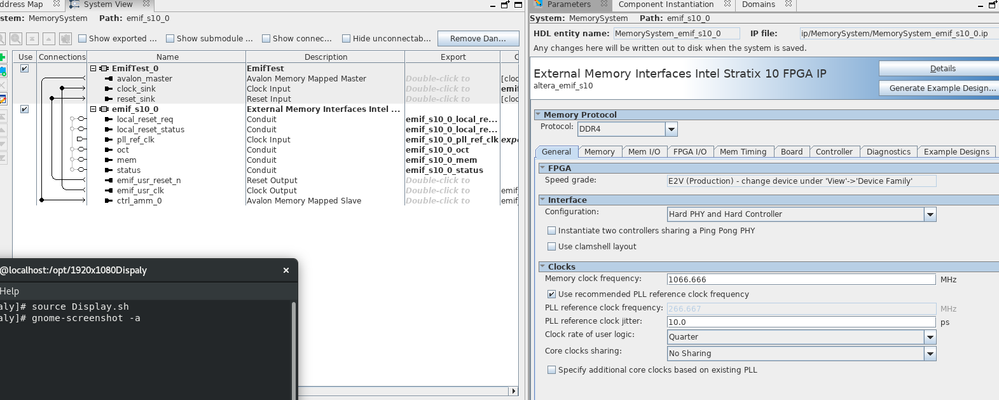

Hi,I have already change my QSYS export as "conduit" . like follow :

but is still report error,thanks for you reply

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

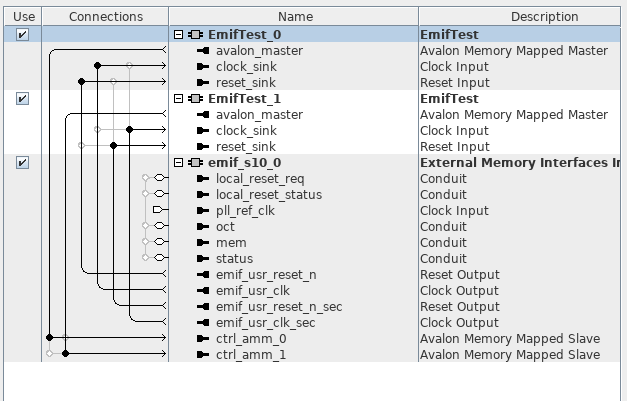

The error message is basically complaining user is not connecting any signal to the amm_* port. Looks like you leave amm_* port floating without connection

- After you export the amm_* port to top level design, did you connect the amm_* to your own user logic ?

- Else you can also connect the amm_* port in platform designer directly to your own user design

If you are still confused, then you can easily generate the example design from EMIF IP directly. After that, open the example design to study the design connection.

Attached is the example design connection reference.

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

after export amm_* port , I am sure I connect it to my own user logic, and it simulation passed. but go to Plan ,it has failed.

Now I change my way, i Encapsulate user logic into IP and add it to platform design it also have same error .

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know which Quartus version that you used ?

Also have you cross check you design with EMIF example design as I suggested ?

If EMIF example design also failed then most likely it's IP bug else it could be something that's not connected correctly in your design.

Thanks.

Regards,

Deshi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I use 19.3 .

yes I have check the example design as you suggested, it passed . but my won design has failed.

Specially,When I Cancelled ping pong Phy , and select DQ width , number of clock, number of chip selects as double to fit my Board , it have passed . but i don't know does it works.

So I very very confused how about my ping pong Phy. Here is my EMIF parameter :

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

Just to confirm are you generating example design with ping pong phy enabled ?

if yes, then that's the best reference for you to debug issue

I know it's tough and tedious but you just need to slowly compare and find out what's the difference between your design and example design.

Alternately, you can also try modify the working example design to remove traffic generator and add in your custom design to see whether it works or not to slowly figure out the problem

- I doubt it's DDR4 IP setting issue. You can try focus to check on the design connection first

- second thing is to check whether you set some weird setting in qsf file that may somehow caused the trouble

Good Luck !

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Thank you very much . I used to do Xilinx FPGA . So I don't Know Intel FPGA Characteristic and Quartus. Sorry I'm in trouble for you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I see.

Np and welcome to Intel FPGA. :)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page