- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am trying to simulate the LVDS Tx and Rx IP cores, but when I run RTL simulation, Modelsim gives an error:

Failed to open design unit file "C:/Users/Sarmad/Documents/Altera/LVDS_Test/LVDS_Rx.vo" in read mode.

The above error occurred when LVDS Tx IP core was instantiated in the project first Rx IP later. If they are instantiated in reverse order, same error is generated for LVDS Tx IP core.

Failed to open design unit file "C:/Users/Sarmad/Documents/Altera/LVDS_Test/LVDS_Tx.vo" in read mode.

Both the IP core simulate fine when simulated individually. The Quartus version I am using is Quartus Prime Lite 18.0, along with Intel FPGA Starter Edition 10.5b.

Would appreciate if someone can help me out. Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes, you are correct I have used ALTLVDS IP core.

I have also used Soft LVDS Intel FPGA IP.

Steps:

- generated Soft LVDS Intel FPGA IP tx & rx individually

- Integrated it into top level HDL file.

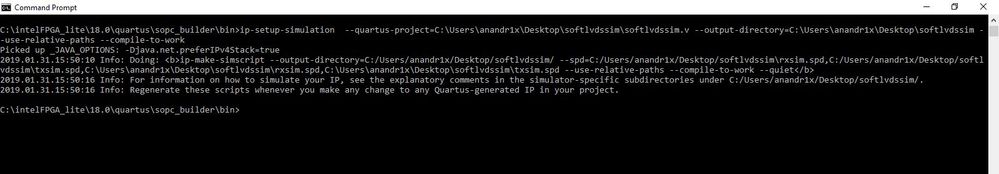

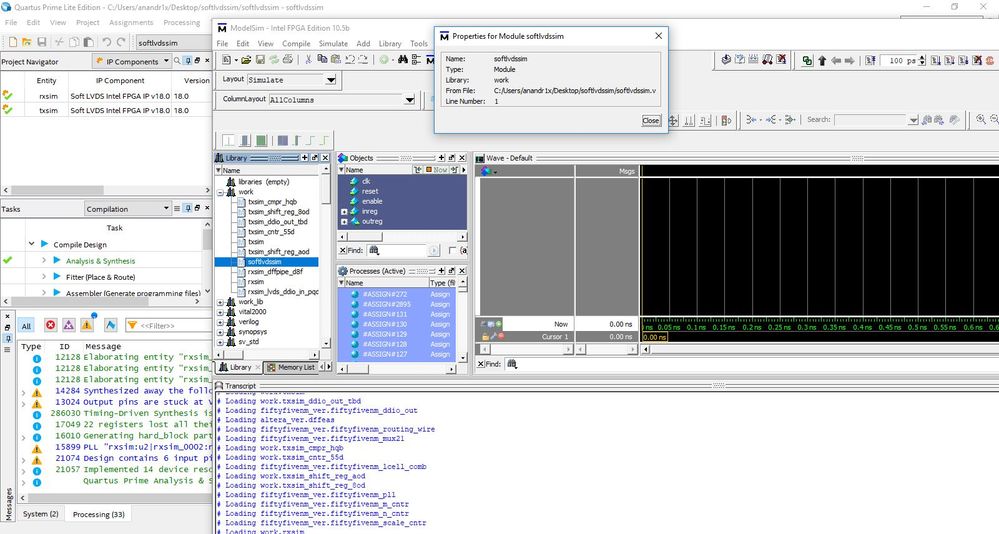

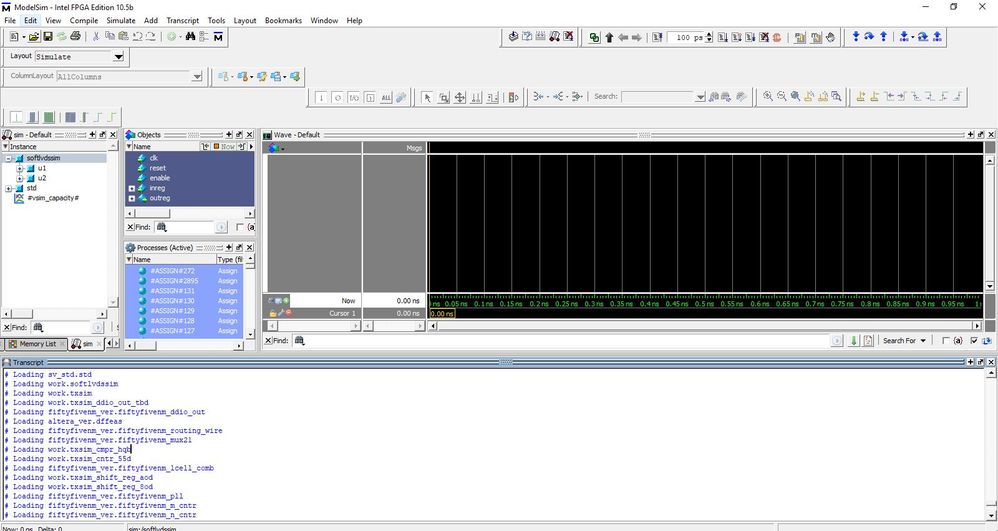

- Generated a combined, version-independent simulation script file including both IP's using ip-setup-simulation command.Attached images

- Create a simple scrip to set top level HDL file and simulate.

Example:

set QSYS_SIMDIR C:/Users/anandr1x/Desktop/softlvdssim

source mentor/msim_setup.tcl

#dev_com

# Override the top-level name (so that elab is useful)

set TOP_LEVEL_NAME softlvdssim

# Compile the standalone IP.

com

# Compile the user top-level vlog -sv ../../top.sv

vlog -sv softlvdssim.v

# Elaborate the design.

elabLet me know if this has helped resolve the issue you are facing or if you need any further assistance.

Regards

Anand

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

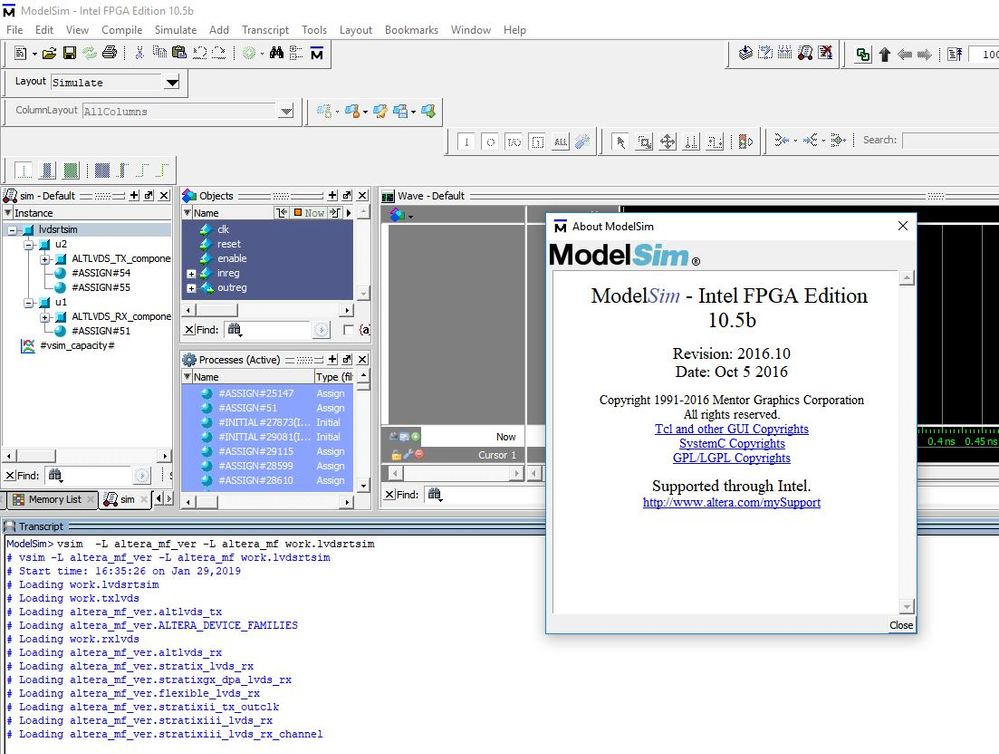

I have just used LVDS Tx and Rx IP initiated in top level HDL file and simulated with out any error.

- order in which IP's are instantiated will not cause any problem.

- In modelsim, i have just compiled top level, Tx & Rx HDL files.

- vsim -L altera_mf_ver -L altera_mf work.lvdsrtsim

Hope it helps.

Let me know if this has helped resolve the issue you are facing or if you need any further assistance.

Regards

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If I am not mistaken did you use ALTLVDS IP core? And isn't it different from the "Soft LVDS Intel FPGA IP"? And I have tried again multiple times but the error persists.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes, you are correct I have used ALTLVDS IP core.

I have also used Soft LVDS Intel FPGA IP.

Steps:

- generated Soft LVDS Intel FPGA IP tx & rx individually

- Integrated it into top level HDL file.

- Generated a combined, version-independent simulation script file including both IP's using ip-setup-simulation command.Attached images

- Create a simple scrip to set top level HDL file and simulate.

Example:

set QSYS_SIMDIR C:/Users/anandr1x/Desktop/softlvdssim

source mentor/msim_setup.tcl

#dev_com

# Override the top-level name (so that elab is useful)

set TOP_LEVEL_NAME softlvdssim

# Compile the standalone IP.

com

# Compile the user top-level vlog -sv ../../top.sv

vlog -sv softlvdssim.v

# Elaborate the design.

elabLet me know if this has helped resolve the issue you are facing or if you need any further assistance.

Regards

Anand

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page