- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I've generated HDL code for the FFT module into a simple project that I'd like to simulate. When I run my .do file for the simulation in Modelsim, however, it fails each time.

Here is a copy of the error:

# Loading work.IFFT_fft_ii_0

# ** Error: (vsim-3033) ./IFFT_fft_ii_0.sv(59): Instantiation of 'asj_fft_dualstream' failed. The design unit was not found.

# Time: 0 ns Iteration: 0 Instance: /CSNEcommAddOn_tb/DUT/u0/fft_ii_0 File: ./IFFT_fft_ii_0.sv

# Searched libraries:

# C:/Users/USERNAME/Documents/HardwareDesign/FPGA/HARDWARE/PROJ/MBS_IFFT/libraries/work

# Error loading design

# Error: Error loading design

# Pausing macro execution

# MACRO ./runlab_CSNEcomm.do PAUSED at line 49I've attached a copy of my *.do script and the *.tcl script that was generated from the IP Core. Not sure if any other info would be helpful though.

Thanks for the help!

- Tags:

- dsp

- fft

- FPGA Intellectual Property

- Intel® FPGA Software Installation & Licensing

- Intel® Quartus® Prime Software

- modelsim

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Have you instantiated the IP core in top level design?

Please refer the below old thread for reference,

https://forums.intel.com/s/question/0D50P00003yyO6LSAU/fft-ip-core-and-modelsim?language=en_US

Try to simulate through the Quartus tool using Native link so that Quartus tool itself will take care of path related issues,

https://www.youtube.com/watch?v=PmVVXQchv2c

would you like to provide your project .*qar file(Project menu->Archive Project...)?

Thanks,

Vicky

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Vicky,

Thanks for the reply. The IP core has been instantiated in the top level design.

I'm trying to re-simulate through the Quartus tool using Native Link like you mentioned, but since I'm using Quartus LITE, the software throws error codes 204012 and 204009, saying that it "Can't generate the netlist output files ..." Looking online, I can disable the error if I avoid using the Native Link.

Is there any other way I can simulate the IP using Native link before deciding whether I'd like to purchase the IP core license?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

"I'm trying to re-simulate through the Quartus tool using Native Link like you mentioned, but since I'm using Quartus LITE, the software throws error codes 204012 and 204009, saying that it "Can't generate the netlist output files ..." Looking online, I can disable the error if I avoid using the Native Link" ---- please refer the link below,

https://www.intel.com/content/www/us/en/programmable/support/support-resources/knowledge-base/solutions/rd12202011_654.html

"Is there any other way I can simulate the IP using Native link before deciding whether I'd like to purchase the IP core license?" ------ You can use 30 days Evaluation period after installation of Quartus tool, please refer the Q.3 from link below,

https://www.intel.com/content/www/us/en/programmable/support/support-resources/download/licensing/q-and-a.html#a_03

Regards,

Vicky

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know any update or should I consider that case to be closed?

Regards,

Vicky

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Vicky,

I followed the youtube video you provided (https://www.youtube.com/watch?v=PmVVXQchv2c) to set up the native link. Doing this I could start modelsim and compile all the libraries.

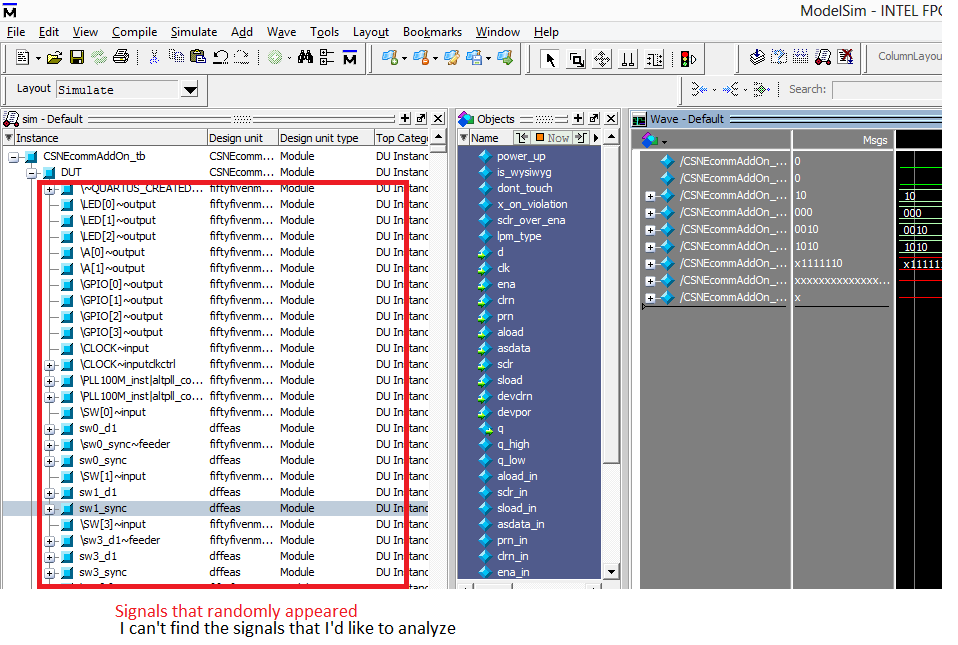

Now when I try to simulate my design modelsim opens, but I cannot add signals from my instantiated modules--the instantiated modules don't show up. In other words, when I try to drag and drop signals into the waveform window, I see the top-level module, and oddly many signals from previous modules that I'm not instantiating, but not any of the other sub-modules. Attached is a screen shot.

Attached is my archived Quartus project as well if that's helpful.

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I started with a new Quartus project, and I can now successfully simulate the FFT IP.

For future users, it is important to add the .sip and .qip files to your project for successful simulation. This can be done by going to Project->Add/Remove Files in Project and then navigating to the files. The .sip file is located in <IP-name>/simulation folder and the .qip file is located in the <IP-name>/synthesis folder. If you don't add these folders and you try to perform Analysis & Synthesis, you will get an error about a missing entity.

Following the youtube video (https://www.youtube.com/watch?v=PmVVXQchv2c) from Intel was also helpful.

For the FFT IP I also had to add <IP-name>.v and one of its submodules to the project for successful Analysis & Synthesis.

Thanks for the help Vicky!

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page