- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Platform: Windows 10, Quartus 20.1 Standard

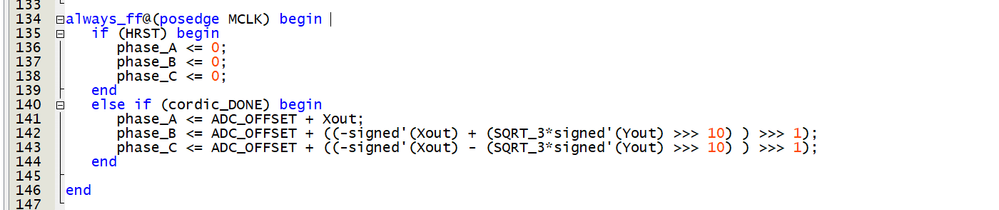

I have a design in which I used the SystemVerilog cast operators, and synthesis failed:

However, when I revert to old style cast operators, the design does compile as shown below:

So I take it that the modern SystemVerilog cast operators do not work, at least on Windows? Can someone at Intel confirm?

Thanks,

James

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

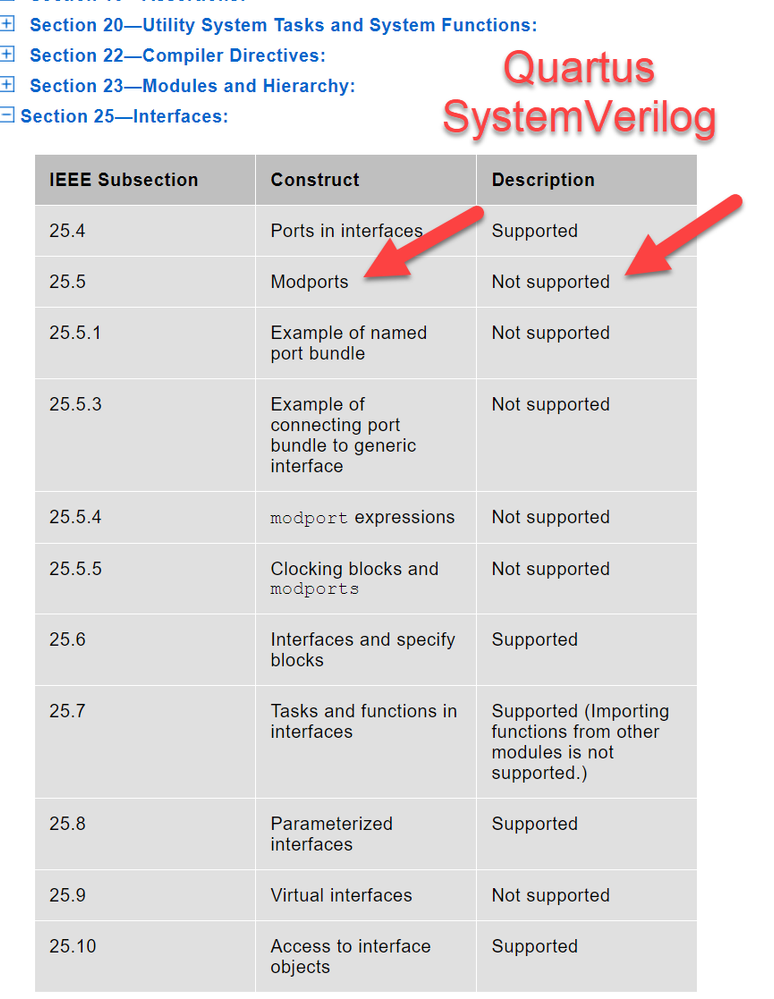

It appears that Quartus does not support SystemVerilog modports, and also is not planning on supporting VHDL 2019 interfaces which support view. Thus, any struct(SystemVerilog) or record(VHDL) must have all members as either in or out direction when using them on a portlist, that is my conclusion to all of this.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What exact error are you getting? This is supported according to the built-in help, so the exact message you're getting might help figure out the issue.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

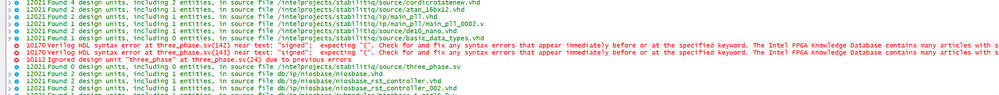

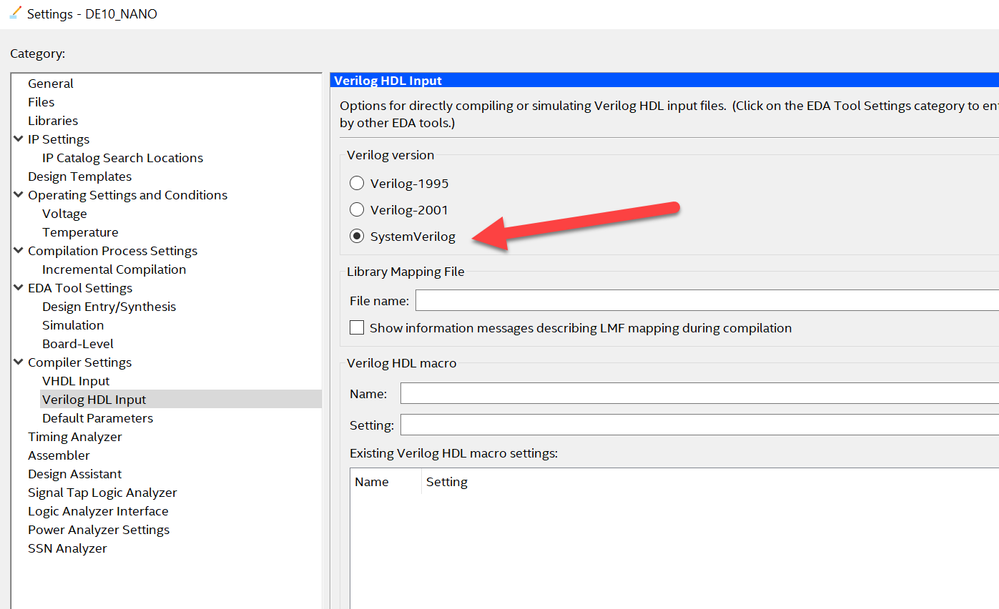

I have a mixed VHDL/SystemVerilog design in Quartus. I made sure the SystemVerilog option was set. Upon compiling, I get the errors shown.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I've never used this before, but is "signed" technically a data type you can convert to with a cast?

https://www.chipverify.com/systemverilog/systemverilog-datatypes

Has it worked elsewhere for you?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, signed and unsigned types are part of SystemVerilog IEEE Standard 1800. Using a tool like Riviera-Pro for simulation, which is old (2018), the cast operator runs fine as I originally showed it working. Only in Quartus does it have an issue.

Looking closer at Quartus SystemVerilog support, it is not as thorough as anticipated. For example, Quartus does not support modports on interfaces in SystemVerilog. So I think you have to look at the detailed aspects of the language to see what is supported in Quartus.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It appears that Quartus does not support SystemVerilog modports, and also is not planning on supporting VHDL 2019 interfaces which support view. Thus, any struct(SystemVerilog) or record(VHDL) must have all members as either in or out direction when using them on a portlist, that is my conclusion to all of this.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page