- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The problem is as follows.

I need a MUX to switch the clock between normal mode and test mode. And I don't care about any transient state when clock switching.

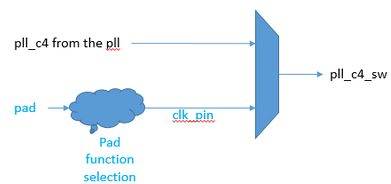

The ending shows the design. 'pll_c4_sw' is the switched output clock. Some IP use 'pll_c4_sw' as a clock. 'pll_c4' is the clock from the PLL. 'clk_pin' is the input clock from the combinational circuit.

( I use ALTPLL to generate pll_c0~pll_c5.

Unfortunately, Quartus13.1 tell me that "PLL "pll|altpll_component|auto_generated|pll1" has parameters clk4_multiply_by and clk4_divide_by specified but port CLK[4] is not connected." when I use the Stratix III device. TimeQuest can't also analysis the timing on pll_c4 becuse TimeQuest can't find pll_c4 which is equal to clk[4] after Fitter.

Could someone please tell me what happen there? Thank you very much.

Design:

assign pll_c4_sw = sel? pll_c4 : clk_pin;

SDC command:

create_generated_clock -name pll_c4 -source [get_pins pll|altpll_component|auto_generated|pll1|inclk[0]] -multiply_by 1 -divide_by 4 [get_pins pll|altpll_component|auto_generated|pll1|clk[4]]

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SyafieqS_Intel, finally, I use the command, /*synthesis keep */, to keep relative port so that TimeQuest can find the CLK[4] port of the PLL.

The CLK[4] port of the PLL in post-fit is "pll|altpll_component|auto_generated|pll1|clk[4]". Thank you, SyafieqS_Intel, very much.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Are you saying the design doesn't synthesize? Maybe you have illegal PLL settings.

Can you show screenshots of the parameter editor (Megawizard)?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sstrell, thank for your suggestion.

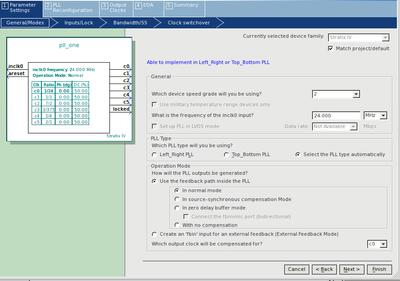

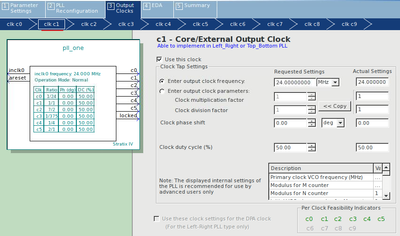

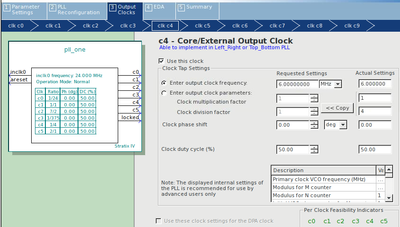

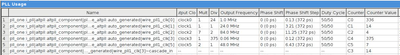

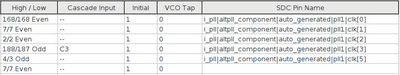

The design can be synthesized and APR. Unfortunately, Quartus13.1 miss the CLK[4] port of PLL after Fitter so that TimeQuest can't find the CLK[4] port of PLL to analysis. Following pictures are the PLL Megawizard and PLL usage. The differences among clocks of PLL only are the multiply parameter and divide parameter. I don't know what's wrong here.

Warning: CLK[4] isn't connected.

PLL Megawizard:

PLL usage:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What is the logic for sel to the mux? If it's not switching, the clock may have been optimized away. As you can see, clock 4 doesn't even show up in the PLL usage report. This is why I suggested previously to add a clock control block and use the switching there instead of creating a mux like this.

You can try to confirm the clock was optimized away by looking at the post-fit Technology Map Viewer and see if you see the clock coming out of the PLL at all. You could also check the compilation report for warning messages about the clock being optimized away or other reasons why it may have disappeared.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sstrell, thank for your suggestion.

The 'sel' signal is from a register. It can be read or write by CPU. The 'sel' signal can be toggled. How to check that Quartus will optimize this signal?

Unfortunately, Quartus tells me that I can't use ALTCLKCTRL Megawizard function to switch clock because Quartus said that the 'clk_pin' signal is from a COMBOUT so that Quartus can't synthesis it. Can I do something else to fix this?

OK, I will try to check in post-fit by the Technology Map Viewer and warning messages. Could you please give some hint about how to check warning messages' by your experience? I only can find the warning message like the following picture when I key in the keyword 'pll*clk'.

Thank you very much.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kfc,

May I know if there is any updates?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SyafieqS_Intel, finally, I use the command, /*synthesis keep */, to keep relative port so that TimeQuest can find the CLK[4] port of the PLL.

The CLK[4] port of the PLL in post-fit is "pll|altpll_component|auto_generated|pll1|clk[4]". Thank you, SyafieqS_Intel, very much.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SyafieqS_Intel, OK, no problem,. Thank you very much.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page