- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

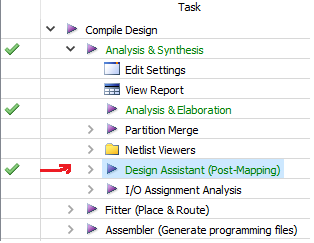

I want to find maximum frequency(or slack time) of an arithmetic operation in Quartus14. But Timequest analyzer, give a Run Fitter before Timequest error, when creating nets. Is there a way without complete place&route, doing timing analysis?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You can create a post-map timing netlist (you have to choose it manually from the Netlist menu in the timing analyzer) and perform an analysis on that, but it won't represent final timing in the design.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You can create a post-map timing netlist (you have to choose it manually from the Netlist menu in the timing analyzer) and perform an analysis on that, but it won't represent final timing in the design.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks @sstrell , I know, there is an option in Vivado. After "synthesis", it's possible to see timing, results change after implementation bevause of routing factors.

But I wasn't sure in Quartus.

Then, as you say, I select post-timing from netlist menu. Netlist loaded in TimeQuest.

Thanks.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page