- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

I have a setup violation at the register after the input register. The input register is constrained as described in AN433.

set_input_delay -add_delay -clock virt_adc_clk -min -0.6 [get_ports {ADC_DATA[*]}]

set_input_delay -add_delay -clock virt_adc_clk -min -0.6 -clock_fall [get_ports {ADC_DATA[*]}]

set_input_delay -add_delay -clock virt_adc_clk -max 0.6 [get_ports {ADC_DATA[*]}]

set_input_delay -add_delay -clock virt_adc_clk -max 0.6 -clock_fall [get_ports {ADC_DATA[*]}]

set_false_path -setup -fall_from [get_clocks virt_adc_clk] -rise_to \

[get_clocks CLK262]

set_false_path -setup -rise_from [get_clocks virt_adc_clk] -fall_to \

[get_clocks CLK262]

set_false_path -hold -rise_from [get_clocks virt_adc_clk] -rise_to \

[get_clocks CLK262]

set_false_path -hold -fall_from [get_clocks virt_adc_clk] -fall_to \

[get_clocks CLK262]But now i have the violation after the input register, as you can see in the picture from Timequest.

Do I miss something?

Link copiado

- « Anterior

-

- 1

- 2

- Próximo »

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

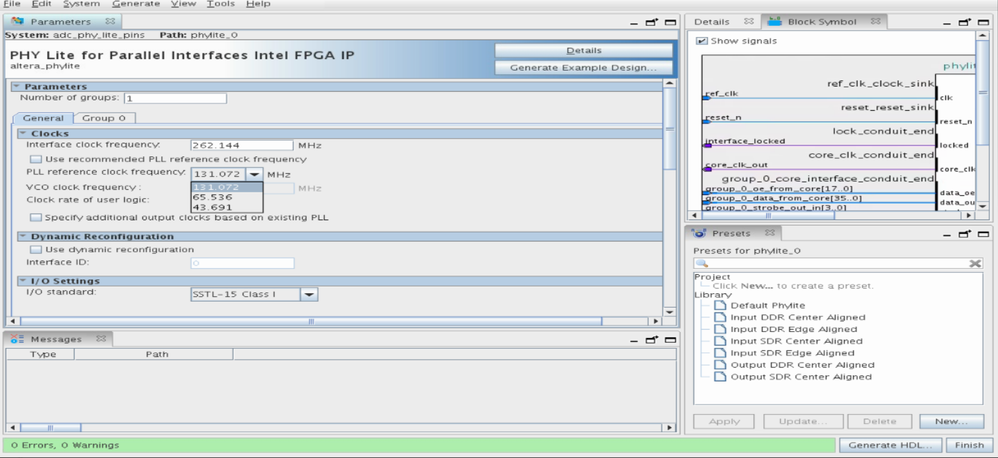

You may connect the 262.144MHz clock to the strobe. The reference clock signal is the reference clock for the PLL where you may set the frequency in the IP Parameter Editor.

Thanks.

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

I tried to add another clock port to the design for the IOPLL. The error is fixed.

Thanks.

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

is there a solution without redesigning the hardware?

Thank you.

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

For design with frequency higher than 200MHz, you have to use PhyLite; and you have to assign a dedicated clock path to the IOPLL.

Thanks.

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

at the moment I'm trying to get the best timing of our hardware, so I use the gpio instead of PhyLite. There I have a routing problem. I used logiclock regions and design partitions to fix the routing.

I set small logiclock regions in front of the ADC pins, the registers after the pins were placed inside the logiclock region, but the pysical routing seems to be strange as you can see on the picture.

There is a negative setup slack on this path. But the hold slack don't need to be that good as it is.

I also added a qar archive.

Can you tell me why the router routes this long way?

Thank you.

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

Please allow me some time to look into this.

Thanks.

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

I tried to remove the logic lock region; the timing is better.

What is the I/O standard you use for the ADC?

Thanks.

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

Logic lock helps in timing but not all the time; it actually depends on the design. I have been working on this for some time and tried different methods to close the timing. Unfortunately, the best result I can get is -0.297ns violation on Slow 900mV -40C Model. Also, I have checked with the team, the suggestion is to use Phylite instead of GPIO for frequency higher than 200MHz. Please use Phylite as this is also suggested in our documentation.

Thanks.

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

An IPS case has been opened for this issue, the case number is 00481849. My colleague will continue to support you through the IPS case.

Thanks.

Best regards,

KhaiY

- Subscrever fonte RSS

- Marcar tópico como novo

- Marcar tópico como lido

- Flutuar este Tópico para o utilizador atual

- Marcador

- Subscrever

- Página amigável para impressora

- « Anterior

-

- 1

- 2

- Próximo »