- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Would you mind show me what causes this error?

Note: I am using Quartus Prime Lite 16.1 to do the exercise that suggests for Quartus® Prime Standard Edition software version 15.1

Below is the piece of code that the error points to.

-- megafunction wizard: %LPM_MULT%

-- GENERATION: STANDARD

-- VERSION: WM1.0

-- MODULE: lpm_mult

-- ============================================================

-- File Name: mult.vhd

-- Megafunction Name(s):

-- lpm_mult

--

-- Simulation Library Files(s):

-- lpm

-- ============================================================

-- ************************************************************

-- THIS IS A WIZARD-GENERATED FILE. DO NOT EDIT THIS FILE!

--

-- 16.1.0 Build 196 10/24/2016 SJ Lite Edition

-- ************************************************************

--Copyright (C) 2016 Intel Corporation. All rights reserved.

--Your use of Intel Corporation's design tools, logic functions

--and other software and tools, and its AMPP partner logic

--functions, and any output files from any of the foregoing

--(including device programming or simulation files), and any

--associated documentation or information are expressly subject

--to the terms and conditions of the Intel Program License

--Subscription Agreement, the Intel Quartus Prime License Agreement,

--the Intel MegaCore Function License Agreement, or other

--applicable license agreement, including, without limitation,

--that your use is for the sole purpose of programming logic

--devices manufactured by Intel and sold by Intel or its

--authorized distributors. Please refer to the applicable

--agreement for further details.

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY lpm;

USE lpm.all;

ENTITY mult IS

PORT

(

clock : IN STD_LOGIC ;

dataa : IN STD_LOGIC_VECTOR (7 DOWNTO 0);

datab : IN STD_LOGIC_VECTOR (7 DOWNTO 0);

result : OUT STD_LOGIC_VECTOR (15 DOWNTO 0)

);

END mult;

ARCHITECTURE SYN OF mult IS

SIGNAL sub_wire0 : STD_LOGIC_VECTOR (15 DOWNTO 0);

COMPONENT lpm_mult

GENERIC (

lpm_hint : STRING;

lpm_pipeline : NATURAL;

lpm_representation : STRING;

lpm_type : STRING;

lpm_widtha : NATURAL;

lpm_widthb : NATURAL;

lpm_widthp : NATURAL

);

PORT (

clock : IN STD_LOGIC ;

dataa : IN STD_LOGIC_VECTOR (7 DOWNTO 0);

datab : IN STD_LOGIC_VECTOR (7 DOWNTO 0);

result : OUT STD_LOGIC_VECTOR (15 DOWNTO 0)

);

END COMPONENT;

BEGIN

result <= sub_wire0(15 DOWNTO 0);

lpm_mult_component : lpm_mult

GENERIC MAP (

lpm_hint => "MAXIMIZE_SPEED=5",

lpm_pipeline => 2,

lpm_representation => "UNSIGNED",

lpm_type => "LPM_MULT",

lpm_widtha => 8,

lpm_widthb => 8,

lpm_widthp => 16

)

PORT MAP (

clock => clock,

dataa => dataa,

datab => datab,

result => sub_wire0

);

END SYN;

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Tri Dang,

Thanks for the all the details.

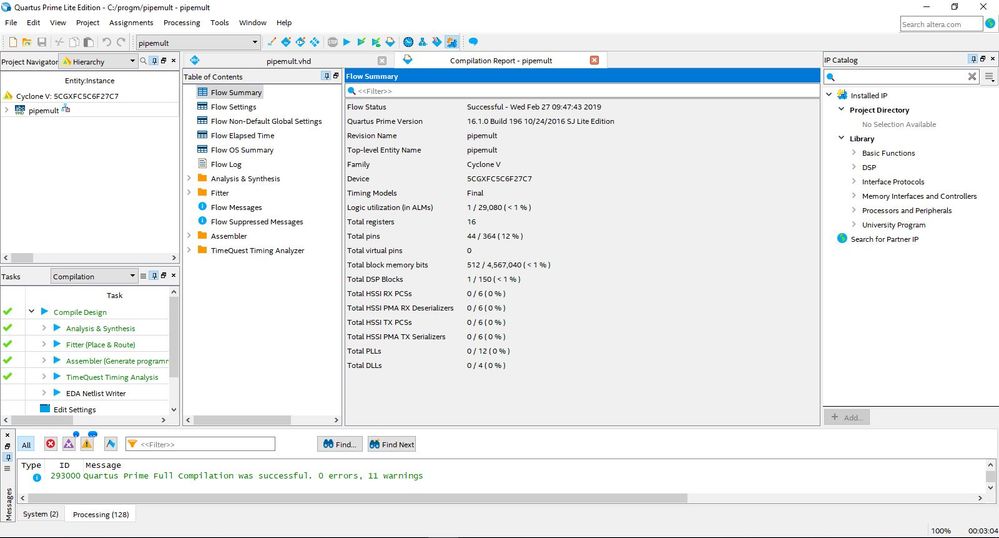

Actually I tried to replicate the issue but I could able to do full compilation,please find the attachment.

1. Can you upgrade the IPs with "Launch the IP upgrade tool" highlighted in yellow colour.

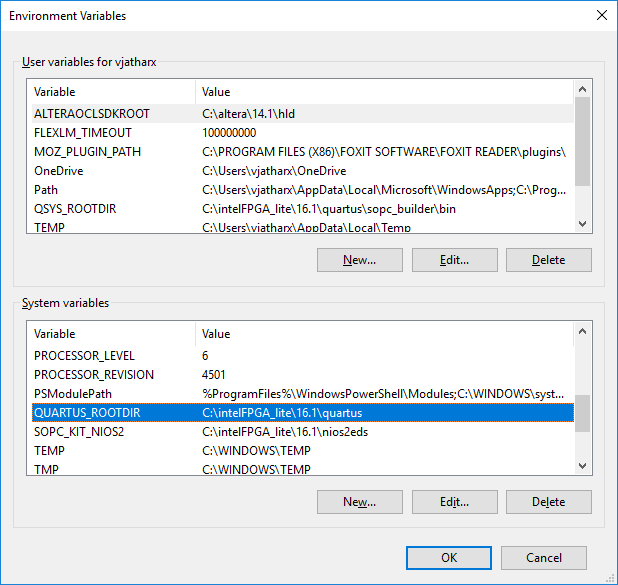

2. Check the Quartus Root Directory,

System-> Advanced System Settings ->Environmental Variables..-> ( to the 16.1 lite)

please let me know if this has helped to resolve the issue.

Regards,

Vikas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It looks like you named the IP "multop" looking at your screenshot which I don't think is the correct name. If the name of the IP and its file doesn't match the top-level as described in the instructions for the lab, you'll get an error.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Vikas,

I cannot open "Advanced System Settings" to check due to my laptop is locked by IT. If you are able to compile this project/exercise with you Quartus 16.1.0 Lite I think I will try it later with different computer.

I don't know if security has anything to do with the error that I had.

I will try this exercise with my home laptop this weekend.

Thanks for your help.

TDang

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page