- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

When I run "get_service_paths master" and "get_service_paths jtag_debug" in the Quartus system console but it yields an empty string. When I open the Quartus Prime Programmer and hit "auto detect", my two JTAG ID's show up. Is there something that needs to be done for my jtag paths to show up in the system console?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What does: get_service_types return?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I ran "get_service_types", then ran "get_service_paths" for each of the service types I found. Here's the results. I bolded the commands that yielded results and underlined the ones that didn't. Let me know if I can provide more information.

%get_service_types

alt_xcvr_custom

alt_xcvr_reconfig_aeq

alt_xcvr_reconfig_dfe

alt_xcvr_reconfig_eye_viewer

alt_xcvr_reconfig_mifwriter

bytestream dashboard

data_pattern_checker

data_pattern_generator

design

device

hard_prbs_checker

hard_prbs_generator

hssiconfig

io_bus issp

jtag_debug

loopback

marker

master

monitor

packet

plugin

processor

slave

sld

trace

trace_db

transceiver_channel_rx

transceiver_channel_tx

transceiver_debug_link

transceiver_reconfig_analog

% get_service_paths alt_xcvr_custom

% get_service_paths alt_xcvr_reconfig_aeq

% get_service_paths alt_xcvr_reconfig_dfe

% get_service_paths alt_xcvr_reconfig_eye_viewer

% get_service_paths alt_xcvr_reconfig_mifwriter

% get_service_paths bytestream

% get_service_paths dashboard

% get_service_paths data_pattern_checker

% get_service_paths data_pattern_generator

% get_service_paths design

% get_service_paths device

/devices/10M04D(A|C)@1#USB-0

% get_service_paths hard_prbs_checker

% get_service_paths hard_prbs_generator

% get_service_paths hssiconfig

% get_service_paths io_bus

% get_service_paths issp

% get_service_paths jtag_debug

% get_service_paths loopback

/devices/10M04D(A|C)@1#USB-0/(link)/JTAG

% get_service_paths marker

/devices/10M04D(A|C)@1#USB-0

% get_service_paths master

% get_service_paths monitor

/design_instances/monitor

% get_service_paths packet

% get_service_paths plugin

/plugins/com.altera.systemconsole.busanalyzer.internal.BusAnalyzerPluginProvider

/plugins/com.altera.systemconsole.dashboard.internal.DashboardPluginProvider

/plugins/com.altera.systemconsole.designs.internal.DesignsPluginProvider

/plugins/com.altera.systemconsole.driver.internal.DriverPluginProvider

/plugins/com.altera.systemconsole.gdbserver.GdbServerPluginProvider

/plugins/com.altera.systemconsole.gui.desktop.DesktopPlugin

/plugins/com.altera.systemconsole.internal.plugin.jtag.JtagPluginProvider

/plugins/com.altera.systemconsole.internal.plugin.jtag.aji.AJIConnectionProvider

/plugins/com.altera.systemconsole.internal.plugin.memory.MemoryPluginProvider

/plugins/com.altera.systemconsole.issp.internal.ISSPPluginProvider

/plugins/com.altera.systemconsole.monitor.internal.MonitorPluginProvider

/plugins/com.altera.systemconsole.plugin.pli.PliDeviceProvider

/plugins/com.altera.systemconsole.scripting.UserScriptSupport

/plugins/com.altera.systemconsole.scripting.ui.ConsolePlugin

/plugins/com.altera.systemconsole.sldhubchannel.SldHubPluginProvider

/plugins/com.altera.systemconsole.tcpchannel.TCPChannelPluginProvider

/plugins/com.altera.systemconsole.toolkit.ToolkitPluginProvider

/plugins/com.altera.systemconsole.trace.drivers.TraceDriversPlugin

/plugins/com.altera.systemconsole.trace.gui.basic.TraceViewMenuPluginProvider

/plugins/com.altera.systemconsole.trace.manager.internal.TraceManagerPluginProvider

/plugins/com.altera.systemconsole.transceivers.internal.TransceiverPluginProvider

/plugins/com.altera.systemconsole.usb.USBConnectionProvider

% get_service_paths processor

% get_service_paths slave

% get_service_paths sld

% get_service_paths trace

% get_service_paths trace_db

% get_service_paths transceiver_channel_rx

% get_service_paths transceiver_channel_tx

% get_service_paths transceiver_debug_link

% get_service_paths transceiver_reconfig_analog

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Does your Platform Designer system design include the JTAG to Avalon bridge or some other bridging component (like a Nios processor)? Without that, you can't use those services.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

That is an excellent question and my gut tells me no. We received the code from the development team with a batch file to download the fpga configuration to the altera chip. I'll look around to see if the project file is in there so I can add a bridge component to the design. Hopefully that'll fix the problem.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

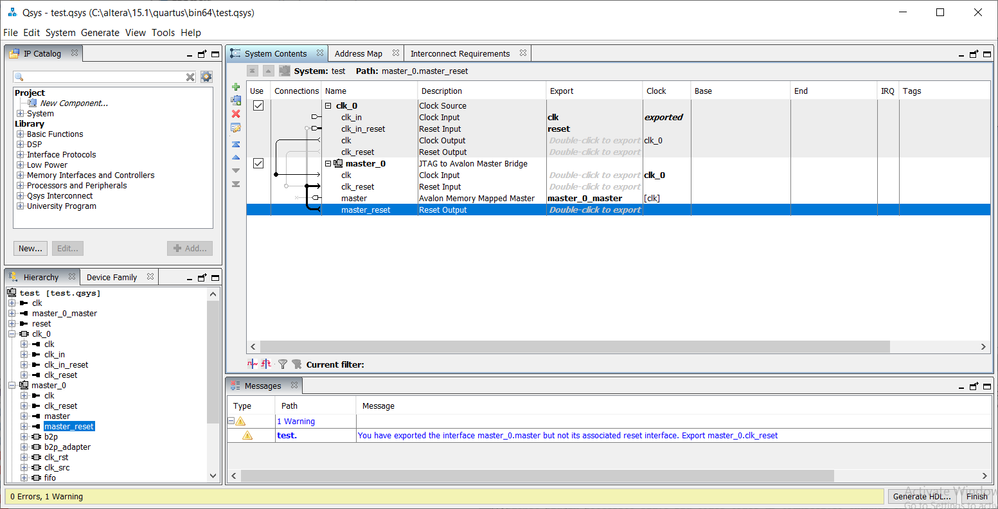

I went into Qsys and added a JTAG to Avalon Master Bridge and saved the test.qsys file with my other quartus files, but when I went to

test "get_service_paths master" I still get nothing. Should I have my .qsys file saved somewhere else? Is there something else I'm missing?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

That system is empty. To use the master service type, you have to connect the host (master) interface to other components in the system. You're just exporting that interface. What's it connected to?

Also, of course, you have to regenerate the system, recompile your Quartus project, and re-program the device.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

So to be clear, we received a board with the Altera chip on it which should have already been configured with the host (master) interface configured. After looking through the batch files we were given they only seem to establish the jtag connection but not upload any configurations to the chip. The fact that we aren't seeing the master service after the board is powered and the jtag connection is established means that we need to open the original project used to compile the fpga in the first place and diagnose what the problem is. Is there anyway to do that without the original project? Thanks for your help so far, this has been immensely useful.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Does the answer from sstrell helps in your case?

It seems that your Platform Designer system is empty/incomplete as mentioned.

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 9/10 survey.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This points me in the correct direction, but I'd like to confirm a path forward towards a solution before I mark anything as a solution yet.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Without the project design files, there's not much you can do.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As this thread has reached a closure, I will now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

Best Regards,

Richard Tan

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 9/10 survey.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page