- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

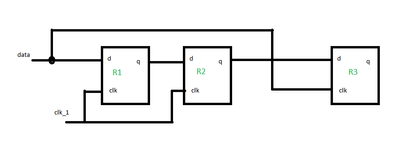

Hello, please help:

async port --- "data"

pll clk --- clk_1

how to set constraints that define difference between delay lines "data ---> R3|clk" and "data --->R1|d"

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You may use set_data_delay, in the timing analyzer you type:

set_data_delay --help

You will see the description on it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

invalid command name "set_data_delay"

quartus 15

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Why would you use that circuit?

How are you going to use the output of R3? In what clock domain? Are you going to run it thru another dual rank synchronizer to access it in clock domain clk_1? Or what?

set_min_delay and set_max_delay are the sdc primitives you can use to constrain the net delays between the referenced ports.

Never heard of set_data_delay. Where is there a reference to that?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

set_data_delay was newly introduce. You may have to use the latest Quartus prime pro to check on it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hmmm. Only latest version of "Quartus Prime Pro" for set_data_delay.

Probably not useful then to 99.9% of people here.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sure.

Since this thread had been answered, we shall close this thread. If you still need further assistance, you are welcome to post a response within 15days. After 15 days, this thread will be transitioned to community support. The community users will be able to help you with your follow-up questions.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page