- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

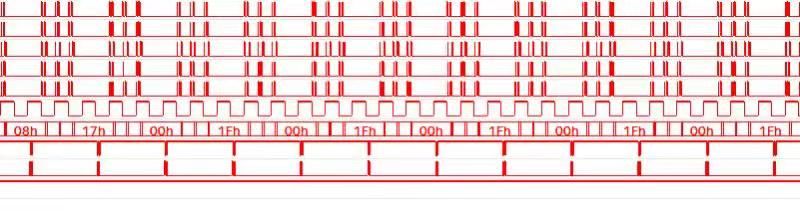

I use cyclone V HPS, and there is a problem in configuring interrupt priority. I gave OSC1 TIMER a higher priority, and after the program was executed, I found that it could not preempt the low priority external interrupt from FPGA. Look at the priority configuration MASK and binary point are lower 3 bits. Excuse me, where is my configuration wrong.

The OSC1 timer runs normally as shown in figure 2. after the interrupt from FPGA is enabled, the timer interrupt cannot run normally, as shown in figure 1

コピーされたリンク

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Is the timer interrupt that you mentioned also could not run normal if if interrupt from other sources other than FPGA?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I didn't try that.

But IRQ from FPGA timer ip doesn't preempt the low priority external interrupt from FPGA pio,too.

So I think something wrong on my configation.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

May I know which Quartus version you are using? Also how did you compile/setup your preloader files?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Please check the ARM document on the Interrupt prioritization:

You can also check out the example design below on GIC controller:

ftp://ftp.intel.com/pub/fpgaup/pub/Intel_Material/16.0/Tutorials/Using_GIC.pdf

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Unfortunately, the link is no longer available.

May I know, how did you setup/configure the prioritization? Did you have the H2f/f2h bridges enabled?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I use this function and I have enabled H2f bridge and light H2F bridge, unuse f2H bridge.

//set prioritization

alt_int_dist_priority_set(ALT_INT_INTERRUPT_F2S_FPGA_IRQ0,48);

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

The Priority interrupts, ID0-ID15, that can only be triggered by software called Software Generated Interrupts (SGI).

Unfortunately, we do not have any official document on how this can be done, thus please refer to below suggestion from other discussion on the SGI configuration:

https://stackoverflow.com/questions/41851975/enable-and-distribute-irqs-in-linux

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I found the documentation below on the Preemption on section 3.3, could you take a look:

https://developer.arm.com/documentation/ihi0048/bb