- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sir

Intel Arria 10 GX (10AX115S2F45I1SG)

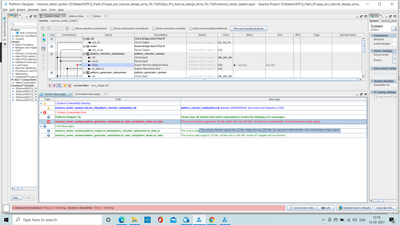

i am getting errors like

The source channel has 32 bits, while sink has 256 bits, for narrow to wide transfer, sink should have "empty" signal.

PFA screen shot.

here sink in ddr4 avalon- memory mapped interface

source is a pattern writer.

My question is how to add an optional empty signal in Avalon- Memory Mapped Interface (already mentioned in Interface Specification) in the sink side which I'm not able to add the Specific Signal in order to resolve the below error attached in the Screen Shot (in platform design).

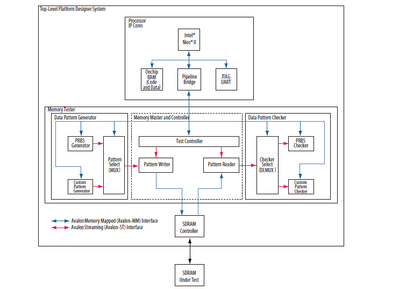

Based on “An 812: Platform Designer System Design tutorial” calibration test done for Nios-2 processor and DDR4.

Now I'm Implementing the remaining modules which includes memory_tester_subsystem and Integrating with DDR 4 where I’m facing Data width mismatch between Pattern Writer which is (32 bits) and DDR4 memory Mapped interface which is (256 bits ) where we need to add the streaming Sink Signal mentioned in platform design.

Link Copied

2 Replies

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Rakesh,

I cant see the error. Could you reattach the snapshot of the error?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SyafieqS_Intel

Thank you for your Response.

Please Find Attached Screen Shot.

reagrds

rakesh

Reply

Topic Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page