- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

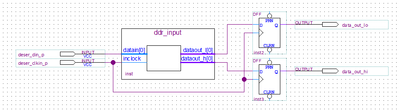

I'm designing a deserializer in Cyclone V and see something strange with a simple ALTDDIO_IN megafunction;

If I leave the clock and data_in ports unassigned the timing analyzer states an Fmax of around 400Mhz which matches up with the datasheet. As soon as I assign physical LVDS pins to the ports the Fmax drops to around 200Mhz. What gives?

Link copiado

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hello,

So you've assigned the pin?

Is it possible that you've seen the Critical Warning mentioned in this KDB: https://www.intel.com/content/www/us/en/support/programmable/articles/000076713.html

May I know which Quartus version you're using?

Thanks,

Nurina

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Yes, I've assigned physical pins, valid LVDS clock and LVDS input. I see no critical warnings. I'm using version 18.1.0.

Thanks for you response,

Greg

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hello,

Can you share your design so I can investigate this further?

Regards,

Nurina

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

I show the design in my original post. I'm not sure what more you need.

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

Please share the .qar file. To generate this, go to Project>Archive Project.

So that I can see what other settings you have applied in the project.

Regards,

Nurina

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

I started to prepare a .qar file by recompiling the project and then ran the timing analyzer one last time. Lo and behold I now get an Fmax around 400Mhz like it should be. I don't know how to explain this. I guess for now the problem is solved.

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hello,

That is odd, but since the problem has been solved I shall close this case. If you have a new question, please login to https://supporttickets.intel.com , view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

p/s: If any answer from community or Intel support are helpful, please feel free to mark as solution, give Kudos and rate 4/5 survey

Regards,

Nurina

- Subscrever fonte RSS

- Marcar tópico como novo

- Marcar tópico como lido

- Flutuar este Tópico para o utilizador atual

- Marcador

- Subscrever

- Página amigável para impressora