- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It would be helpful if you could tell us the following points about the rden signal input to the RAM block.

1) Reading is valid when rden is 'H', but is the read address latched even if rden is 'L'?

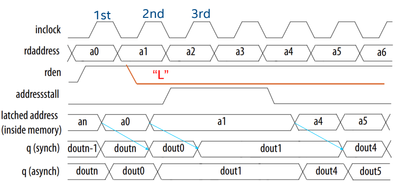

2) In Figures 7 to 11 on page 41 of the user guide, q becomes Hi-Z at the rising edge of the next clock after rden becomes 'L'. In Figure 4 on page 16, is it correct to assume that dout0 of q(synch) is not the contents of read address "a1" when rden becomes 'L' at read address "a1"?

3) In Figure 4 on page 16, there are doutn-1 and doutn in q(synch), but will data be read even if rden is 'L'? RAM has 2 ports and will be used in "With one read port and one write port" mode. Clocking is "Dual clock: use separate 'read' and 'write' clocks".

In addition, please forgive me that it is a sentence of machine translation that is not in English. Sorry for the inconvenience, but thank you in advance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, the data output retains the previous values that are held during the most recent active read enable. Which is dout0.

You can see the same thing in figure 4 as well.

No worry. I am happy to help.

Best Regards,

Richard Tan

p/s: Please do expert delay in response due to lunar new year.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you add a link to the document you are referring to?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your comment.

The document I am referring to is UG-01068 Embedded Memory (RAM: 1-PORT, RAM: 2-PORT, ROM: 1-PORT, and ROM: 2-PORT) User Guide.

The link is

becomes.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1) No, the read address do not latched when rden is L. It is this (addressstall = 1) signal that holds the previous address value for as long as the signal is enabled.

2) I don't get the meaning or the motivation behind the first sentence "In Figures 7 to 11 on page 41 of the user guide, q becomes Hi-Z at the rising edge of the next clock after rden becomes 'L'." I will answer the question for figure 4 instead - the question is a bit weird, it feel like asking two different things in one question... probably due to the translation I guess, but I will try to answer as best as possible.

dout0 is not the contents of read address a1, it is the contents from address a0. data N out from address N.

dout0 is the data that was read in the first clock cycle at address a0. So if rden become L at address a1, the q (synch) will still be dout0 at 2nd clock cycle as it was already read in the 1st clock cycle. But since the address a1 is not read in the 2nd clock cycle, the data at the next or 3rd clock cycle will retain as data dout0.

3) As explained in Q2, data would not be read if rden is low. If you create the read-enable port and perform a write operation (with the read enable port deasserted ), the data output port retains the previous values that are held during the most recent active read enable. Likewise, if you activate the read enable during a write operation, the output port shows the new data being written, the old data at that address, or a “Don't Care” value when read-during-write occurs at the same address location.

Best Regards,

Richard Tan

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

p/s: Please do expert delay in response due to lunar new year.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your detailed explanation.

I recognized that the read address is not latched when RDEN is 'L', and the data of the last latched address during the period when RDEN is 'H' is output at the next clock.

In the figure you posted, a0 is latched at 1st CLK and selection of dout0 is completed, so rden is 'L' at 2nd CLK, but q(synch) outputs dout0.

Is it correct to understand that q(synch) continues to output dout0 when rden is 'L' after the 3rd CLK?

We apologize for the inconvenience, but thank you in advance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, the data output retains the previous values that are held during the most recent active read enable. Which is dout0.

You can see the same thing in figure 4 as well.

No worry. I am happy to help.

Best Regards,

Richard Tan

p/s: Please do expert delay in response due to lunar new year.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your answer.

Thanks to you, I was able to solve the problem.

Thank you for your kind response.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for acknowledge the solution provided.

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, Please login to https://supporttickets.intel.com, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

Thank you.

Best Regards,

Richard Tan

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page