- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Target: Agilex

Tools version: Quartus Pro 21.3

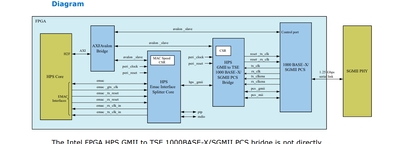

We are trying to implement this diagram found in the “Embedded Peripherals IP User Guide” to convert a HPS EMAC to SGMII interface coming from the E-tile. We can successfully add the splitter core and the SGMII PCS bridge on the FPGA, but are having trouble adding the 1000 BASE-X/SGMII PCS on the E-Tile

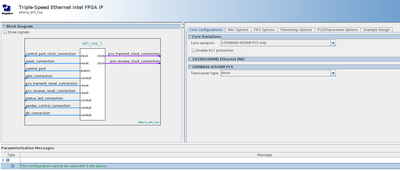

On the same user guide it mentions that the 1000 BASE-X/SGMII PCS comes from the Triple-Speed Ethernet core but when adding the core in platform designer as a PCS only the program mentions that the configuration can’t be used in the E-tile. It only allows it in the E-tile when choosing an Ethernet MAC without PCS configuration, which is not what we want as we are designing to use the HPS EMAC.

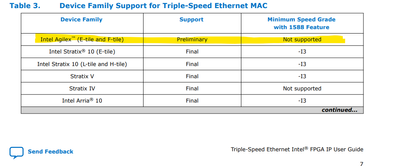

Another detail is that the triple-speed ethernet core document mentions that the Agilex E-tile support is “preliminary”. What does that mean?

Let me know if there are any suggestions

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The E-tile cannot support the 1GbE. It has hard blocks supporting 10G/25G and 100G only.

The logic that you generate through this IP will mostly be implemented in the FPGA fabric for an E-tile device.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the reply

I am not planning on using MAC from the E-Tile. Instead I want to use the EMAC from the HPS and just use the E-Tile in pass-through mode for SGMII PCS

You are saying just using the SGMII PCS only is then not supported on the E-Tile hardened IP? Even if I were to use it for 10GE it would show that I can't use SGMII PCS only mode

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am saying that 1 Gbps is not possible to implement in E-Tile as the hard blocks do not support.

E-tile is capable of implementing either 10G / 25G or 100G logic. See the architecture diagram in the link sent previously. It is self-explanatory.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The document you linked says that the transceivers on the E-tile support NRZ all the way down to 1 Gbps, no? SGMII is 1.25 Gbps, so it seems like it should be possible to use PMA direct mode to implement SGMII. Obviously the MAC and PCS logic would have to be bypassed, and the SGMII PCS and gigabit MAC implemented in fabric logic, but I don't see any reason why this wouldn't be possible with the E-tile transceivers.

https://www.intel.com/content/www/us/en/docs/programmable/683723/current/supported-features.html

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

In your original query you enquired about the TSE IP, which does not have a PMA only option.

If you use E-tile XCVR PHY IP at 1Gbps data rate, the PCS and MAC should be implemented in the FPGA fabric. There is no PCS available in this IP.

If using TSE IP, you can use the hard IP for 10G/25G and 100G data rates only.

Hope this clarifies.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As the query has been answered, closing the ticket. However, it will still be open for community users to comment.

Regards

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page