- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

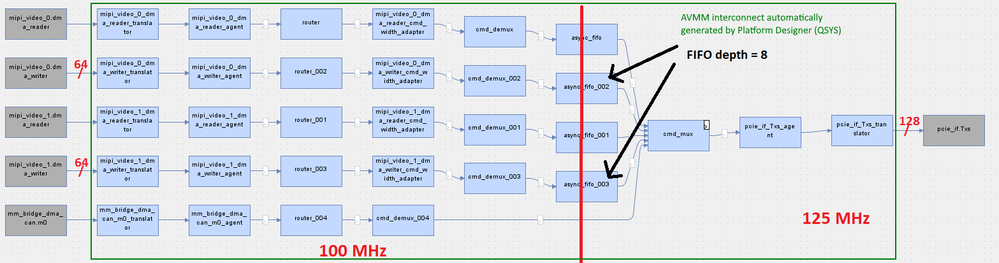

We connect multiple AvalonMM masters to the Arria V Avalon MM PCIe IP. Qsys automatically creates an appropiate AVMM interconnect which looks as follows:

Two Avalon masters (called dma_writer in the above image) have data width 64 bit, run at 100 MHz and simultaneously perform burst write transactions of 32 words. The input of the PCIe IP has data width 128 bits and runs at 125 MHz.

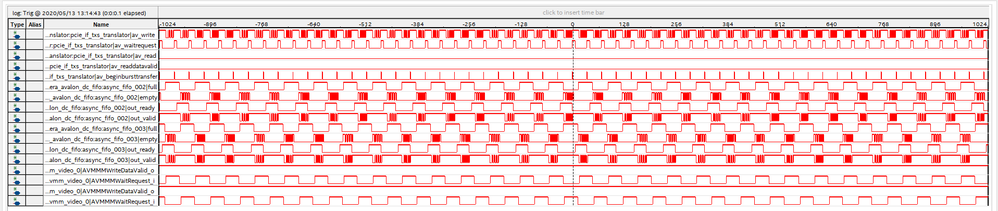

Because the data sink (PCIe IP) runs at a higher clock freuqency than the data sources there should be no bottleneck inside the interconnect. Signal tap analyis revealed however that there is a bottleneck caused by the asyncronous FIFOs. Because they have only depth 8 they can only buffer very few data (not even 1 burst) while the cmd_mux streams data from the other AVMM master.

How can we solve this problem? We could solve this issue be manually inserting an AVMM clock crossing bridge but are interested in a solution where Qsys automatically creates the entire interconnect.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You could manually add FIFOs instead of the ones chosen by PD and set them to whatever depth you need. That's probably the easiest thing to do.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Fabien,

Yes, the simplest what I could think to solve this issue right now is to implement Avalon-MM Clock Crossing Bridge IP. It transfers Avalon-MM commands and responses between different clock domain and parameters to control the depth of the command and response FIFOs in both the master and slave clock domains.

Thanks,

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Manually inserting Avalon-MM Clock Crossing Bridge IP did solve the problem but this solution complicates the design and uses more FPGA ressources.

Because the automatic generation of interconnects is the main feature of QSYS I would expect it to behave more intelligent. Based on what information does QSYS decide how deep the asyncronous FIFOs in the interconnect are? Is it possible to influence the FIFO depth be changing the parameters of the AVMM masters and slaves in the hw_tcl files?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Fabien,

You can create and edit you own component for _hw.tcl file and have flexibility to control the parameter according to your desires. You cannot edit components installed with the Quartus II software, such as Altera-provided components Refer to link below for creating PD component.

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-qpp-platform-designer.pdf (p89- Creating Platform Designer Components).

Thanks,

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For the blocks to the left in the above picture (called dma_reader and dma_writer) we wrote our own component _hw.tcl files. Here a snippet of the _hw.tcl file of the dma_writer:

add_interface dma_output avalon start

set_interface_property dma_output addressUnits SYMBOLS

set_interface_property dma_output associatedClock clk

set_interface_property dma_output associatedReset clr

set_interface_property dma_output bitsPerSymbol 8

set_interface_property dma_output burstOnBurstBoundariesOnly false

set_interface_property dma_output burstcountUnits WORDS

set_interface_property dma_output doStreamReads false

set_interface_property dma_output doStreamWrites false

set_interface_property dma_output holdTime 0

set_interface_property dma_output linewrapBursts false

set_interface_property dma_output maximumPendingReadTransactions 0

set_interface_property dma_output maximumPendingWriteTransactions 0

set_interface_property dma_output readLatency 0

set_interface_property dma_output readWaitTime 1

set_interface_property dma_output setupTime 0

set_interface_property dma_output timingUnits Cycles

set_interface_property dma_output writeWaitTime 0

set_interface_property dma_output ENABLED true

set_interface_property dma_output EXPORT_OF ""

set_interface_property dma_output PORT_NAME_MAP ""

set_interface_property dma_output CMSIS_SVD_VARIABLES ""

set_interface_property dma_output SVD_ADDRESS_GROUP ""

add_interface_port dma_output AVMMMWriteDataValid_o write Output 1

add_interface_port dma_output AVMMMWriteData_o writedata Output OUT_DATA_WIDTH_G

add_interface_port dma_output AVMMMBurstCount_o burstcount Output 6

add_interface_port dma_output AVMMMAddress_o address Output 64

add_interface_port dma_output AVMMMWaitRequest_i waitrequest Input 1Is there a way to achieve a larger FIFO depth in the automatically generated interconnect by changing the parameters of the components connected to the interconnect? I would like that an entire burst of 32 words fits into the FIFOs.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Fabien,

Refer to link below FIFO Intel® FPGA IP User Guide

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_fifo.pdf ( p3-Configuration Methods)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The FIFO is inside an AVMM interconnect that is automatically generated by Platform Designed (QSYS). Please refer to the image in the first post to study the setup.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Fabien,

Could you resend the design file for me to check it via private check/email

Thanks,

Regards

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page