- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hey guys,

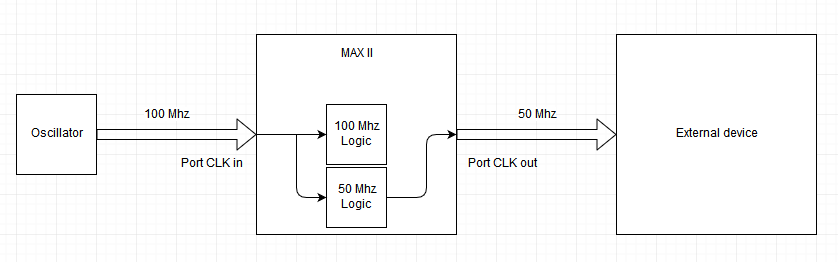

what is a safe way to realize the behaviour in the picture below without using a PLL (because there is none in MAX II device)....

Should i generate a Clock enable ? How do i do this realiably in VERILOG ?

Thanks for you help !!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You really don't provide enough background info for a detailed answer. How are the clocks for the 100MHz and 50MHz domains generated?

To meet some external timing constraints you should write constraints for the layout that express your restrictions and then Quartus will attempt to meet these and it will tell you if it can't in the timing report.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hey thanks for your answer so far. The 100 Mhz are from an external oscillator crystal and feed into one of the dedicated clock inputs of the CPLD, i need to divide this clock to 50 Mhz in the CPLD to use it as clock source for another external device.... is this possible in any reliable way ?

... Actually while iam writing this and think about it there might be no really reliable way to do this without PLL :/ but maybe iam wrong.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In the MaxII architecture that is about the only way to do it. 100MHz clock comes in on a clock pin, distribute and use as CLK100. Use that to clock a divide by 2 FF to generate signal CLK50, and use that as the clock for your 50MHz logic. Quartus will assign CLK100 and CLK50 to high fanout, low skew routing. The on CLK50 register the signals that you want to drive DIRECTLY to the output pin nodes. This will give you the fastest clock to output delay. Drive outputs directly, don't add any logic functions (and, or, etc) between the register outputs and the output pins. And as I said add timing constraints to the design to guide Quartus layout, and validate that your device will meet your timing requirements.

BTW the MaxII is a REALLY old family at this point. It should NOT be used in any new design, but only if you are reusing some existing legacy boards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Agree

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page