- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

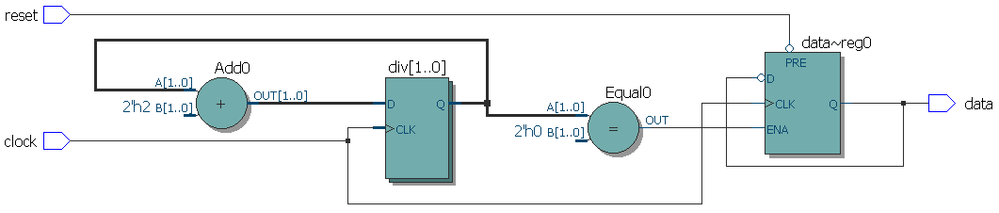

Consider the following code:

Is there any way to tell Quartus to create clock enable signal within any clock use in clkena_test module? The workaround could be opening clkena_test.v file, and manually add if(clkena) into every always construct. But this would not work if I use auto-generated IP which may be overwritten by the tool, and thus all changes will get lost. Note: gated clock is NOT a solution.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You can use if-generate or case-generate and a parameter to do this in any submodule.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I do not understand, please give example. I have this situation with remote update (generated by Quartus megawizard) which can not run at 120 MHz, and need to lower the clock speed 8 times, still keeping the remote update clock synchronized with main design clock (passing data within same clock domain) - and looking for easiest solution, which, from my point of view, using clock enable. But remote update IP does not have clock enable input to it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

So your question is a little unclear.

You're not asking specifically about clkena_test, the test code you posted. You're talking about instantiating an IP that does not include a clock enable input and you're asking how to add clock enable to something that doesn't have it. Is that correct?

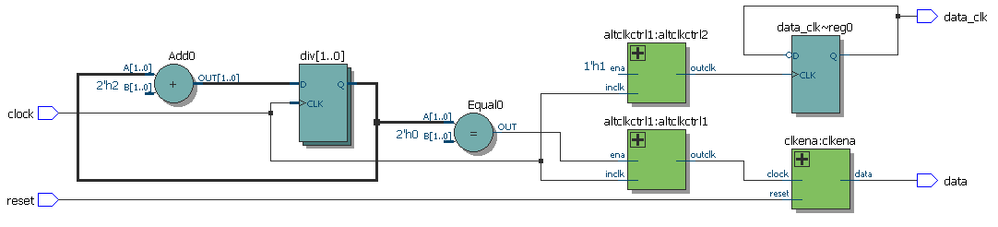

If I'm interpreting this correctly, then you need to use a clock gate. But don't gate the clock directly. Use a clock control block (altclkctrl) IP, which includes an option for clock enable. Then feed the output of the clock control block to the IP that does not include clock enable.

If I'm still not interpreting this correctly, perhaps you can include a diagram or something to better explain exactly what you want/need.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@sstrell wrote:

You're talking about instantiating an IP that does not include a clock enable input and you're asking how to add clock enable to something that doesn't have it. Is that correct?

Yes, and target design is remote update.

@sstrell wrote:

If I'm interpreting this correctly, then you need to use a clock gate. But don't gate the clock directly. Use a clock control block (altclkctrl) IP, which includes an option for clock enable. Then feed the output of the clock control block to the IP that does not include clock enable.

I am using altclkctrl in another design selecting master frequency for MP3 playback. But I am not sure if the circuit based on altclkcrtl will have output clock in the same clock domain as its input clock, and if it will appear that they are guaranteed to be synchronized, what will be final clock delay, and in which direction.

My main module, which connects remote update, uses master clock of e.g. 120 MHz. Remote update needs slower clock. Let's say these 120 MHz divided by 4 or 8 (just as an example). And I need both circuits to be fully synchronized to be able to pass multiwire data between them without metastability, ideally not using synchronizers or cross-domain handshaking (using some scarce silicon).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

So use a clock control block or a separate PLL. You might also need multicycle timing exceptions in your .sdc file to line up the setup and hold timing correctly.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you very much! I have several questions left:

1. how many clock controllers can be set up in Cyclone 3? They seem using dedicated logic, but I can not find this information in the documentation;

2. should I pass both master clock, and slower clock through clock controllers for compensate for the delays in them? (see below)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The things may be more complicated than I thought before. Analyzing the remote update block documentation I do not see any specification for the clock. I see only clock speed up to 40 MHz and that it must be "valid". Nothing about clock duty cycle. And unfortunately, implementing the clocking using clock enable turns clock to duty cycle other than 50%, and pulse width will be the same as original clock at 120 MHz. Within the "remote_update" module clock connects to "cycloneiii_rublock", and I can not find any information on it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I decided to go the other route changing the architecture rather than considering more and more complex clocking problem. Now I use one control signal using synchronizer, and ensure that data is held several cycles after synchronizer finishes to ensure set up and hold times are not violated when circuit driving remote update latches the data.

Thanks for your help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @EugenyB

It seems to me that you have find a solution.

Could you help to confirm and let me know if you need further help in regards to this case?

Best Regards,

Richard Tan

p/s: If any answer from the community or Intel support are helpful, please feel free to give Kudos.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have yet to receive any response from you but I believed that you have found a solution to your question.

With that, I will now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

Best Regards,

Richard Tan

p/s: If any answer from the community or Intel support are helpful, please feel free to give Kudos.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page