- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I run the project "LL10G_1G_10G_LINESIDE_1588v2" on the demo board "Arria 10 SOC Development Kit"

1588V2 thranceive an receive are OK ; I made project run on my board(10AS066H3F34I2SG) , it is cannot receive anything .

can the chip "10AS066H3F34I2SG" surport the 1588v2 ?

% TEST_1588 0 1 10G

CONFIGURE CHANNEL 0 as master

configure_to_10G

setting up mac with a basic working config

setting 0xC5C4 into rxmac primary address Reg-1

setting 0xC3C2C1C0 into rxmac primary address Reg-0

enabling: pad and crc stripping in rx mac

testing Configure Period and Adjustment RX XGMII TSU

Configure Period and Adjustment TX XGMII TSU

clearing mac stats registers

testing Configure Period and Adjustment RX XGMII TSU

Configure Period and Adjustment TX XGMII TSU

Configure TOD Master

Configure TOD 10G

Disabling serial PMA Loopback (local)

Read back Serial PMA loopback register = 0x00000000

CONFIGURE CHANNEL 1 as slave

configure_to_10G

setting up mac with a basic working config

setting 0xC5C4 into rxmac primary address Reg-1

setting 0xC3C2C1C0 into rxmac primary address Reg-0

enabling: pad and crc stripping in rx mac

testing Configure Period and Adjustment RX XGMII TSU

Configure Period and Adjustment TX XGMII TSU

clearing mac stats registers

testing Configure Period and Adjustment RX XGMII TSU

Configure Period and Adjustment TX XGMII TSU

Configure TOD Master

Configure TOD 10G

Disabling serial PMA Loopback (local)

Read back Serial PMA loopback register = 0x00000000

Select 1588 traffic controller

Start TOD synchronization

Master 1588 start 1 step operation

TRAFFIC_CONTROLLER_BASE_ADDR: 0x100000

Waiting capturing offset delay ...

-- Break

Start capturing offset delay ...

Reset Master 1588 start 1 step operation

Reset Start TOD synchronization

delay ns = 0x00000000

delay fns = 0x00000000

offset ns = 0x00000000

offset fns = 0x00000000

===================================================================

| MAC TX STATS REGISTER CHECK

===================================================================

|# FRAMES_RECEIVED_WITH_ERROR = 0

|# UNICAST_FRAMES_WITH_ERROR = 0

|# MULTICAST_FRAMES_RECEIVED_WITH_ERROR = 0

|# BRDCAST_FRAMES_WITH_ERROR = 0

|# FRAMES_RECEIVED_WITH_ONLY_CRCERROR = 0

|# VALID_LENGTH_FRAMES_WITH_CRC_ERROR = 0

|# JABBER_FRAMES = 0

|# FRAGMENTED_FRAMES = 0

|# INVALID_FRAMES_RECEIVED = 0

|# FRAMES_RECEIVED_GOOD = 0

|# PAUSE_FRAMES_RECEIVED = 0

|# UNICAST_CONTROL_FRAMES = 0

|# MULTICAST_CONTROL_FRAMES = 0

|# UNICAST_FRAMES_RECEIVED_GOOD = 0

|# MULTICAST_FRAMES_RECEIVED_GOOD = 0

|# BRDCAST_FRAMES_GOOD = 0

|# DATA_AND_PADDING_OCTETS_RECEIVED_GOOD= 0

|# COMPREHENSICE_OCTETS_RECEIVED = 0

|# FRAMES_WITH_SIZE_64_BYTES = 0

|# FRAMES_BETWEEN_SIZE_64AND127_BYTES = 0

|# FRAMES_BETWEEN_SIZE_128AND255_BYTES = 0

|# FRAMES_BETWEEN_SIZE_256AND511_BYTES = 0

|# FRAMES_BETWEEN_SIZE_512AND1K_BYTES = 0

|# FRAMES_BETWEEN_SIZE_1KND1518_BYTES = 0

======================================================================

| MAC RX STATS REGISTER CHECK

======================================================================

|# FRAMES_RECEIVED_WITH_ERROR = 0

|# UNICAST_FRAMES_WITH_ERROR = 0

|# MULTICAST_FRAMES_RECEIVED_WITH_ERROR = 0

|# BRDCAST_FRAMES_WITH_ERROR = 0

|# FRAMES_RECEIVED_WITH_ONLY_CRCERROR = 0

|# VALID_LENGTH_FRAMES_WITH_CRC_ERROR = 0

|# JABBER_FRAMES = 0

|# FRAGMENTED_FRAMES = 0

|# INVALID_FRAMES_RECEIVED = 0

|# FRAMES_RECEIVED_GOOD = 0

|# PAUSE_FRAMES_RECEIVED = 0

|# UNICAST_CONTROL_FRAMES = 0

|# MULTICAST_CONTROL_FRAMES = 0

|# UNICAST_FRAMES_RECEIVED_GOOD = 0

|# MULTICAST_FRAMES_RECEIVED_GOOD = 0

|# BRDCAST_FRAMES_GOOD = 0

|# DATA_AND_PADDING_OCTETS_RECEIVED_GOOD= 0

|# COMPREHENSICE_OCTETS_RECEIVED = 0

|# FRAMES_WITH_SIZE_64_BYTES = 0

|# FRAMES_BETWEEN_SIZE_64AND127_BYTES = 0

|# FRAMES_BETWEEN_SIZE_128AND255_BYTES = 0

|# FRAMES_BETWEEN_SIZE_256AND511_BYTES = 0

|# FRAMES_BETWEEN_SIZE_512AND1K_BYTES = 0

|# FRAMES_BETWEEN_SIZE_1KND1518_BYTES = 0

|# FRAMES_BETWEEN_SIZE_ABOVE1519_BYTES = 0

===================================================================

| MAC TX STATS REGISTER CHECK

===================================================================

|# FRAMES_RECEIVED_WITH_ERROR = 0

|# UNICAST_FRAMES_WITH_ERROR = 0

|# MULTICAST_FRAMES_RECEIVED_WITH_ERROR = 0

|# BRDCAST_FRAMES_WITH_ERROR = 0

|# FRAMES_RECEIVED_WITH_ONLY_CRCERROR = 0

|# VALID_LENGTH_FRAMES_WITH_CRC_ERROR = 0

|# JABBER_FRAMES = 0

|# FRAGMENTED_FRAMES = 0

|# INVALID_FRAMES_RECEIVED = 0

|# FRAMES_RECEIVED_GOOD = 0

|# PAUSE_FRAMES_RECEIVED = 0

|# UNICAST_CONTROL_FRAMES = 0

|# MULTICAST_CONTROL_FRAMES = 0

|# UNICAST_FRAMES_RECEIVED_GOOD = 0

|# MULTICAST_FRAMES_RECEIVED_GOOD = 0

|# BRDCAST_FRAMES_GOOD = 0

|# DATA_AND_PADDING_OCTETS_RECEIVED_GOOD= 0

|# COMPREHENSICE_OCTETS_RECEIVED = 0

|# FRAMES_WITH_SIZE_64_BYTES = 0

|# FRAMES_BETWEEN_SIZE_64AND127_BYTES = 0

|# FRAMES_BETWEEN_SIZE_128AND255_BYTES = 0

|# FRAMES_BETWEEN_SIZE_256AND511_BYTES = 0

|# FRAMES_BETWEEN_SIZE_512AND1K_BYTES = 0

|# FRAMES_BETWEEN_SIZE_1KND1518_BYTES = 0

======================================================================

| MAC RX STATS REGISTER CHECK

======================================================================

|# FRAMES_RECEIVED_WITH_ERROR = 0

|# UNICAST_FRAMES_WITH_ERROR = 0

|# MULTICAST_FRAMES_RECEIVED_WITH_ERROR = 0

|# BRDCAST_FRAMES_WITH_ERROR = 0

|# FRAMES_RECEIVED_WITH_ONLY_CRCERROR = 0

|# VALID_LENGTH_FRAMES_WITH_CRC_ERROR = 0

|# JABBER_FRAMES = 0

|# FRAGMENTED_FRAMES = 0

|# INVALID_FRAMES_RECEIVED = 0

|# FRAMES_RECEIVED_GOOD = 0

|# PAUSE_FRAMES_RECEIVED = 0

|# UNICAST_CONTROL_FRAMES = 0

|# MULTICAST_CONTROL_FRAMES = 0

|# UNICAST_FRAMES_RECEIVED_GOOD = 0

|# MULTICAST_FRAMES_RECEIVED_GOOD = 0

|# BRDCAST_FRAMES_GOOD = 0

|# DATA_AND_PADDING_OCTETS_RECEIVED_GOOD= 0

|# COMPREHENSICE_OCTETS_RECEIVED = 0

|# FRAMES_WITH_SIZE_64_BYTES = 0

|# FRAMES_BETWEEN_SIZE_64AND127_BYTES = 0

|# FRAMES_BETWEEN_SIZE_128AND255_BYTES = 0

|# FRAMES_BETWEEN_SIZE_256AND511_BYTES = 0

|# FRAMES_BETWEEN_SIZE_512AND1K_BYTES = 0

|# FRAMES_BETWEEN_SIZE_1KND1518_BYTES = 0

|# FRAMES_BETWEEN_SIZE_ABOVE1519_BYTES = 0

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello mark_lee,

Thank you for posting in Intel Ethernet Communities.

Your query will be best answered by our Intel Field Programmable Gate Array (FPGA) Support team, we will help you to move this post to the designated team for further assistance.

Please feel free to contact us if you need assistance from Intel Ethernet support team.

May you have a great day!

Best regards,

Crisselle C

Intel® Customer Support

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi TEAM

In addition: demo board "Arria 10 SOC Development Kit" use the chip"10AS066N3F40E2SG";

my project use the chip "10AS066H3F34I2SG

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

May I know which Ethernet ref design that you are referring here ?

- Any download link or do explain to me how you generate the ref design ?

Typically 1588 feature follow Ethernet IP and has less dependency on FPGA device speedgrade. Since both A10 SOC dev kit and your board are using Arria 10 FPGA, it should work.

Which means the failure is either due to Quartus design issue, board setup issue or board design issue. The good news is you at least have a golden working ref design on A10 SOC dev kit board. You just need to compare and find out the difference that may caused the failure.

- To rule out Quartus design issue

- I presume you use back same ref design without changes to the RTL design ?

- Does the design met Quartus timequest timing closure ?

- Also pls verify the qsf setting particularly on pin location and IO standard setting to match with your own board

- To rule out board setup issue

- Pls double check on FPGA reset, power and clocking

- Your log file shown zero Tx and Rx transaction where I suspect either your design is stuck in reset or clocking is not provided correctly

- Or maybe some FPGA pin location or IO standard is set wrongly

- To rule out board design issue

- Can your board handle 10G data transfer without concern on signal integrity issue ?

- Have you try to use transceiver toolkit to perform loopback testing on your board to verify 10G signal transfer is good on your board first ?

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Deshi ant team

1. The Project "LL10G_1G_10G_LINESIDE_1588v2" is builded Reference the Intel Example "a10soc_322265325_Scalable_Eth1588_BUG2613_Quartus_16.1.0";

2. My Project is working on the Quartus Prime pro 19.2;

3.I have running my project on my board ,"TEST_SMA_LB 0 1 10G " is ok;

4.I have running my project on my board ,"TEST_PHYSERIA_LOOPBACK " is ok;

5.When finish TEST_PHYSERIAL_LOOPBACK , and running“TEST_1588 0 1 10G" right now,sometime frames received is good , "offset ns" and "delay ns" are good , but when runningTEST_1588 again it is receive annything 。

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Deshi ant team

In addition:

1. "TEST_SMA_LB 0 10 G 5000 " and "TEST_PHYSERIAL_LOOPBACK "1 10G 5000" are ok, message is :

(1)

% TEST_SMA_LB 0 10G 5000

CONFIGURE CHANNEL 0

configure_to_10G

setting up mac with a basic working config

setting 0xC5C4 into rxmac primary address Reg-1

setting 0xC3C2C1C0 into rxmac primary address Reg-0

enabling: pad and crc stripping in rx mac

testing Configure Period and Adjustment RX XGMII TSU

Configure Period and Adjustment TX XGMII TSU

clearing mac stats registers

testing Configure Period and Adjustment RX XGMII TSU

Configure Period and Adjustment TX XGMII TSU

Configure TOD Master

Configure TOD 10G

Disabling serial PMA Loopback (local)

Read back Serial PMA loopback register = 0x00000000

Select std ethernet traffic controller

Disable Avalon ST Loopback

====================================================================================

B E G I N C O N F I G U R A T I O N

====================================================================================

payload length = fixed ....

payload bytes = fixed incremental bytes ....

burst size = 5000 ....

payload length = 100 ....

frame source addres field = F0F1F2F3F4F5 ....

frame destination addres field = C5C4C3C2C1C0 ....

reseting monitor Packet Counters

number of Packets Expected By Monitor = 0x1388

burst being injected into device ....

-- MONITOR processing frames received .....

-- MONITOR Received Packet# 5000]

-- DONE! - monitor received all expected sum of packets .....

_________________________________________________________________________________________________________________________

-- (MONITOR) GOOD PKTS RECEIVED = 5000

-- (MONITOR) BAD PKTS RECEIVED = 0

-- (MONITOR) BYTES RECEIVED = 479992

-- (MONITOR) CYCLES USED = 75002

-- (MONITOR) THROUGHPUT CALCULATED = 8.00 Gbps

-- (MONITOR) RXBYTECNT_LO32 = 479992

-- (MONITOR) RXBYTECNT_HI32 = 0

-- (MONITOR) RXCYCLCNT_LO32 = 75002

-- (MONITOR) RXCYCLCNT_HI32 = 0

_________________________________________________________________________________________________________________________

===================================================================

| MAC TX STATS REGISTER CHECK

===================================================================

|# FRAMES_RECEIVED_WITH_ERROR = 0

|# UNICAST_FRAMES_WITH_ERROR = 0

|# MULTICAST_FRAMES_RECEIVED_WITH_ERROR = 0

|# BRDCAST_FRAMES_WITH_ERROR = 0

|# FRAMES_RECEIVED_WITH_ONLY_CRCERROR = 0

|# VALID_LENGTH_FRAMES_WITH_CRC_ERROR = 0

|# JABBER_FRAMES = 0

|# FRAGMENTED_FRAMES = 0

|# INVALID_FRAMES_RECEIVED = 0

|# FRAMES_RECEIVED_GOOD = 5000

|# PAUSE_FRAMES_RECEIVED = 0

|# UNICAST_CONTROL_FRAMES = 0

|# MULTICAST_CONTROL_FRAMES = 0

|# UNICAST_FRAMES_RECEIVED_GOOD = 0

|# MULTICAST_FRAMES_RECEIVED_GOOD = 5000

|# BRDCAST_FRAMES_GOOD = 0

|# DATA_AND_PADDING_OCTETS_RECEIVED_GOOD= 410000

|# COMPREHENSICE_OCTETS_RECEIVED = 500000

|# FRAMES_WITH_SIZE_64_BYTES = 0

|# FRAMES_BETWEEN_SIZE_64AND127_BYTES = 5000

|# FRAMES_BETWEEN_SIZE_128AND255_BYTES = 0

|# FRAMES_BETWEEN_SIZE_256AND511_BYTES = 0

|# FRAMES_BETWEEN_SIZE_512AND1K_BYTES = 0

|# FRAMES_BETWEEN_SIZE_1KND1518_BYTES = 0

======================================================================

| MAC RX STATS REGISTER CHECK

======================================================================

|# FRAMES_RECEIVED_WITH_ERROR = 0

|# UNICAST_FRAMES_WITH_ERROR = 0

|# MULTICAST_FRAMES_RECEIVED_WITH_ERROR = 0

|# BRDCAST_FRAMES_WITH_ERROR = 0

|# FRAMES_RECEIVED_WITH_ONLY_CRCERROR = 0

|# VALID_LENGTH_FRAMES_WITH_CRC_ERROR = 0

|# JABBER_FRAMES = 0

|# FRAGMENTED_FRAMES = 0

|# INVALID_FRAMES_RECEIVED = 0

|# FRAMES_RECEIVED_GOOD = 5000

|# PAUSE_FRAMES_RECEIVED = 0

|# UNICAST_CONTROL_FRAMES = 0

|# MULTICAST_CONTROL_FRAMES = 0

|# UNICAST_FRAMES_RECEIVED_GOOD = 0

|# MULTICAST_FRAMES_RECEIVED_GOOD = 5000

|# BRDCAST_FRAMES_GOOD = 0

|# DATA_AND_PADDING_OCTETS_RECEIVED_GOOD= 410000

|# COMPREHENSICE_OCTETS_RECEIVED = 500000

|# FRAMES_WITH_SIZE_64_BYTES = 0

|# FRAMES_BETWEEN_SIZE_64AND127_BYTES = 5000

|# FRAMES_BETWEEN_SIZE_128AND255_BYTES = 0

|# FRAMES_BETWEEN_SIZE_256AND511_BYTES = 0

|# FRAMES_BETWEEN_SIZE_512AND1K_BYTES = 0

|# FRAMES_BETWEEN_SIZE_1KND1518_BYTES = 0

|# FRAMES_BETWEEN_SIZE_ABOVE1519_BYTES = 0

(2)

% TEST_PHYSERIAL_LOOPBACK 1 10G 5000

CONFIGURE CHANNEL 1

configure_to_10G

setting up mac with a basic working config

setting 0xC5C4 into rxmac primary address Reg-1

setting 0xC3C2C1C0 into rxmac primary address Reg-0

enabling: pad and crc stripping in rx mac

testing Configure Period and Adjustment RX XGMII TSU

Configure Period and Adjustment TX XGMII TSU

clearing mac stats registers

testing Configure Period and Adjustment RX XGMII TSU

Configure Period and Adjustment TX XGMII TSU

Configure TOD Master

Configure TOD 10G

Disabling serial PMA Loopback (local)

Read back Serial PMA loopback register = 0x00000000

Enabling serial PMA Loopback (local)

Read back Serial PMA loopback register = 0x00000001

Select std ethernet traffic controller

Disable Avalon ST Loopback

====================================================================================

B E G I N C O N F I G U R A T I O N

====================================================================================

payload length = fixed ....

payload bytes = fixed incremental bytes ....

burst size = 5000 ....

payload length = 100 ....

frame source addres field = F0F1F2F3F4F5 ....

frame destination addres field = C5C4C3C2C1C0 ....

reseting monitor Packet Counters

number of Packets Expected By Monitor = 0x1388

burst being injected into device ....

-- MONITOR processing frames received .....

-- MONITOR Received Packet# 5000]

-- DONE! - monitor received all expected sum of packets .....

_________________________________________________________________________________________________________________________

-- (MONITOR) GOOD PKTS RECEIVED = 5000

-- (MONITOR) BAD PKTS RECEIVED = 0

-- (MONITOR) BYTES RECEIVED = 479992

-- (MONITOR) CYCLES USED = 75002

-- (MONITOR) THROUGHPUT CALCULATED = 8.00 Gbps

-- (MONITOR) RXBYTECNT_LO32 = 479992

-- (MONITOR) RXBYTECNT_HI32 = 0

-- (MONITOR) RXCYCLCNT_LO32 = 75002

-- (MONITOR) RXCYCLCNT_HI32 = 0

_________________________________________________________________________________________________________________________

===================================================================

| MAC TX STATS REGISTER CHECK

===================================================================

|# FRAMES_RECEIVED_WITH_ERROR = 0

|# UNICAST_FRAMES_WITH_ERROR = 0

|# MULTICAST_FRAMES_RECEIVED_WITH_ERROR = 0

|# BRDCAST_FRAMES_WITH_ERROR = 0

|# FRAMES_RECEIVED_WITH_ONLY_CRCERROR = 0

|# VALID_LENGTH_FRAMES_WITH_CRC_ERROR = 0

|# JABBER_FRAMES = 0

|# FRAGMENTED_FRAMES = 0

|# INVALID_FRAMES_RECEIVED = 0

|# FRAMES_RECEIVED_GOOD = 5000

|# PAUSE_FRAMES_RECEIVED = 0

|# UNICAST_CONTROL_FRAMES = 0

|# MULTICAST_CONTROL_FRAMES = 0

|# UNICAST_FRAMES_RECEIVED_GOOD = 0

|# MULTICAST_FRAMES_RECEIVED_GOOD = 5000

|# BRDCAST_FRAMES_GOOD = 0

|# DATA_AND_PADDING_OCTETS_RECEIVED_GOOD= 410000

|# COMPREHENSICE_OCTETS_RECEIVED = 500000

|# FRAMES_WITH_SIZE_64_BYTES = 0

|# FRAMES_BETWEEN_SIZE_64AND127_BYTES = 5000

|# FRAMES_BETWEEN_SIZE_128AND255_BYTES = 0

|# FRAMES_BETWEEN_SIZE_256AND511_BYTES = 0

|# FRAMES_BETWEEN_SIZE_512AND1K_BYTES = 0

|# FRAMES_BETWEEN_SIZE_1KND1518_BYTES = 0

======================================================================

| MAC RX STATS REGISTER CHECK

======================================================================

|# FRAMES_RECEIVED_WITH_ERROR = 0

|# UNICAST_FRAMES_WITH_ERROR = 0

|# MULTICAST_FRAMES_RECEIVED_WITH_ERROR = 0

|# BRDCAST_FRAMES_WITH_ERROR = 0

|# FRAMES_RECEIVED_WITH_ONLY_CRCERROR = 0

|# VALID_LENGTH_FRAMES_WITH_CRC_ERROR = 0

|# JABBER_FRAMES = 0

|# FRAGMENTED_FRAMES = 0

|# INVALID_FRAMES_RECEIVED = 0

|# FRAMES_RECEIVED_GOOD = 5000

|# PAUSE_FRAMES_RECEIVED = 0

|# UNICAST_CONTROL_FRAMES = 0

|# MULTICAST_CONTROL_FRAMES = 0

|# UNICAST_FRAMES_RECEIVED_GOOD = 0

|# MULTICAST_FRAMES_RECEIVED_GOOD = 5000

|# BRDCAST_FRAMES_GOOD = 0

|# DATA_AND_PADDING_OCTETS_RECEIVED_GOOD= 410000

|# COMPREHENSICE_OCTETS_RECEIVED = 500000

|# FRAMES_WITH_SIZE_64_BYTES = 0

|# FRAMES_BETWEEN_SIZE_64AND127_BYTES = 5000

|# FRAMES_BETWEEN_SIZE_128AND255_BYTES = 0

|# FRAMES_BETWEEN_SIZE_256AND511_BYTES = 0

|# FRAMES_BETWEEN_SIZE_512AND1K_BYTES = 0

|# FRAMES_BETWEEN_SIZE_1KND1518_BYTES = 0

|# FRAMES_BETWEEN_SIZE_ABOVE1519_BYTES = 0

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Deshi ant team

1. I do some test forward the step :

(1) "TEST_PHYSERIAL_LOOPBACK 1 10G 5000” ,is OK

(2) “TEST_1588 0 1 10G ” is OK

(3) "TEST_1588 0 1 10G" again, is not OK

2. The console system print message is :

% TEST_PHYSERIAL_LOOPBACK 1 10G 5000

CONFIGURE CHANNEL 1

configure_to_10G

setting up mac with a basic working config

setting 0xC5C4 into rxmac primary address Reg-1

setting 0xC3C2C1C0 into rxmac primary address Reg-0

enabling: pad and crc stripping in rx mac

testing Configure Period and Adjustment RX XGMII TSU

Configure Period and Adjustment TX XGMII TSU

clearing mac stats registers

testing Configure Period and Adjustment RX XGMII TSU

Configure Period and Adjustment TX XGMII TSU

Configure TOD Master

Configure TOD 10G

Disabling serial PMA Loopback (local)

Read back Serial PMA loopback register = 0x00000000

Enabling serial PMA Loopback (local)

Read back Serial PMA loopback register = 0x00000001

Select std ethernet traffic controller

Disable Avalon ST Loopback

====================================================================================

B E G I N C O N F I G U R A T I O N

====================================================================================

payload length = fixed ....

payload bytes = fixed incremental bytes ....

burst size = 5000 ....

payload length = 100 ....

frame source addres field = F0F1F2F3F4F5 ....

frame destination addres field = C5C4C3C2C1C0 ....

reseting monitor Packet Counters

number of Packets Expected By Monitor = 0x1388

burst being injected into device ....

-- MONITOR processing frames received .....

-- MONITOR Received Packet# 5000]

-- DONE! - monitor received all expected sum of packets .....

_________________________________________________________________________________________________________________________

-- (MONITOR) GOOD PKTS RECEIVED = 5000

-- (MONITOR) BAD PKTS RECEIVED = 0

-- (MONITOR) BYTES RECEIVED = 479992

-- (MONITOR) CYCLES USED = 75002

-- (MONITOR) THROUGHPUT CALCULATED = 8.00 Gbps

-- (MONITOR) RXBYTECNT_LO32 = 479992

-- (MONITOR) RXBYTECNT_HI32 = 0

-- (MONITOR) RXCYCLCNT_LO32 = 75002

-- (MONITOR) RXCYCLCNT_HI32 = 0

_________________________________________________________________________________________________________________________

===================================================================

| MAC TX STATS REGISTER CHECK

===================================================================

|# FRAMES_RECEIVED_WITH_ERROR = 0

|# UNICAST_FRAMES_WITH_ERROR = 0

|# MULTICAST_FRAMES_RECEIVED_WITH_ERROR = 0

|# BRDCAST_FRAMES_WITH_ERROR = 0

|# FRAMES_RECEIVED_WITH_ONLY_CRCERROR = 0

|# VALID_LENGTH_FRAMES_WITH_CRC_ERROR = 0

|# JABBER_FRAMES = 0

|# FRAGMENTED_FRAMES = 0

|# INVALID_FRAMES_RECEIVED = 0

|# FRAMES_RECEIVED_GOOD = 5000

|# PAUSE_FRAMES_RECEIVED = 0

|# UNICAST_CONTROL_FRAMES = 0

|# MULTICAST_CONTROL_FRAMES = 0

|# UNICAST_FRAMES_RECEIVED_GOOD = 0

|# MULTICAST_FRAMES_RECEIVED_GOOD = 5000

|# BRDCAST_FRAMES_GOOD = 0

|# DATA_AND_PADDING_OCTETS_RECEIVED_GOOD= 410000

|# COMPREHENSICE_OCTETS_RECEIVED = 500000

|# FRAMES_WITH_SIZE_64_BYTES = 0

|# FRAMES_BETWEEN_SIZE_64AND127_BYTES = 5000

|# FRAMES_BETWEEN_SIZE_128AND255_BYTES = 0

|# FRAMES_BETWEEN_SIZE_256AND511_BYTES = 0

|# FRAMES_BETWEEN_SIZE_512AND1K_BYTES = 0

|# FRAMES_BETWEEN_SIZE_1KND1518_BYTES = 0

======================================================================

| MAC RX STATS REGISTER CHECK

======================================================================

|# FRAMES_RECEIVED_WITH_ERROR = 0

|# UNICAST_FRAMES_WITH_ERROR = 0

|# MULTICAST_FRAMES_RECEIVED_WITH_ERROR = 0

|# BRDCAST_FRAMES_WITH_ERROR = 0

|# FRAMES_RECEIVED_WITH_ONLY_CRCERROR = 0

|# VALID_LENGTH_FRAMES_WITH_CRC_ERROR = 0

|# JABBER_FRAMES = 0

|# FRAGMENTED_FRAMES = 0

|# INVALID_FRAMES_RECEIVED = 0

|# FRAMES_RECEIVED_GOOD = 5000

|# PAUSE_FRAMES_RECEIVED = 0

|# UNICAST_CONTROL_FRAMES = 0

|# MULTICAST_CONTROL_FRAMES = 0

|# UNICAST_FRAMES_RECEIVED_GOOD = 0

|# MULTICAST_FRAMES_RECEIVED_GOOD = 5000

|# BRDCAST_FRAMES_GOOD = 0

|# DATA_AND_PADDING_OCTETS_RECEIVED_GOOD= 410000

|# COMPREHENSICE_OCTETS_RECEIVED = 500000

|# FRAMES_WITH_SIZE_64_BYTES = 0

|# FRAMES_BETWEEN_SIZE_64AND127_BYTES = 5000

|# FRAMES_BETWEEN_SIZE_128AND255_BYTES = 0

|# FRAMES_BETWEEN_SIZE_256AND511_BYTES = 0

|# FRAMES_BETWEEN_SIZE_512AND1K_BYTES = 0

|# FRAMES_BETWEEN_SIZE_1KND1518_BYTES = 0

|# FRAMES_BETWEEN_SIZE_ABOVE1519_BYTES = 0

% TEST_1588 0 1 10G

CONFIGURE CHANNEL 0 as master

configure_to_10G

setting up mac with a basic working config

setting 0xC5C4 into rxmac primary address Reg-1

setting 0xC3C2C1C0 into rxmac primary address Reg-0

enabling: pad and crc stripping in rx mac

testing Configure Period and Adjustment RX XGMII TSU

Configure Period and Adjustment TX XGMII TSU

clearing mac stats registers

testing Configure Period and Adjustment RX XGMII TSU

Configure Period and Adjustment TX XGMII TSU

Configure TOD Master

Configure TOD 10G

Disabling serial PMA Loopback (local)

Read back Serial PMA loopback register = 0x00000000

CONFIGURE CHANNEL 1 as slave

configure_to_10G

setting up mac with a basic working config

setting 0xC5C4 into rxmac primary address Reg-1

setting 0xC3C2C1C0 into rxmac primary address Reg-0

enabling: pad and crc stripping in rx mac

testing Configure Period and Adjustment RX XGMII TSU

Configure Period and Adjustment TX XGMII TSU

clearing mac stats registers

testing Configure Period and Adjustment RX XGMII TSU

Configure Period and Adjustment TX XGMII TSU

Configure TOD Master

Configure TOD 10G

Disabling serial PMA Loopback (local)

Read back Serial PMA loopback register = 0x00000000

Select 1588 traffic controller

Start TOD synchronization

Master 1588 start 1 step operation

TRAFFIC_CONTROLLER_BASE_ADDR: 0x100000

Waiting capturing offset delay ...

-- Break

Start capturing offset delay ...

Reset Master 1588 start 1 step operation

Reset Start TOD synchronization

delay ns = 0x00000030

delay fns = 0x00007197

offset ns = 0x00000000

offset fns = 0x00000000

===================================================================

| MAC TX STATS REGISTER CHECK

===================================================================

|# FRAMES_RECEIVED_WITH_ERROR = 0

|# UNICAST_FRAMES_WITH_ERROR = 0

|# MULTICAST_FRAMES_RECEIVED_WITH_ERROR = 0

|# BRDCAST_FRAMES_WITH_ERROR = 0

|# FRAMES_RECEIVED_WITH_ONLY_CRCERROR = 0

|# VALID_LENGTH_FRAMES_WITH_CRC_ERROR = 0

|# JABBER_FRAMES = 0

|# FRAGMENTED_FRAMES = 0

|# INVALID_FRAMES_RECEIVED = 0

|# FRAMES_RECEIVED_GOOD = 9120026

|# PAUSE_FRAMES_RECEIVED = 0

|# UNICAST_CONTROL_FRAMES = 0

|# MULTICAST_CONTROL_FRAMES = 0

|# UNICAST_FRAMES_RECEIVED_GOOD = 9120026

|# MULTICAST_FRAMES_RECEIVED_GOOD = 0

|# BRDCAST_FRAMES_GOOD = 0

|# DATA_AND_PADDING_OCTETS_RECEIVED_GOOD= 456001300

|# COMPREHENSICE_OCTETS_RECEIVED = 620161768

|# FRAMES_WITH_SIZE_64_BYTES = 4560013

|# FRAMES_BETWEEN_SIZE_64AND127_BYTES = 4560013

|# FRAMES_BETWEEN_SIZE_128AND255_BYTES = 0

|# FRAMES_BETWEEN_SIZE_256AND511_BYTES = 0

|# FRAMES_BETWEEN_SIZE_512AND1K_BYTES = 0

|# FRAMES_BETWEEN_SIZE_1KND1518_BYTES = 0

======================================================================

| MAC RX STATS REGISTER CHECK

======================================================================

|# FRAMES_RECEIVED_WITH_ERROR = 0

|# UNICAST_FRAMES_WITH_ERROR = 0

|# MULTICAST_FRAMES_RECEIVED_WITH_ERROR = 0

|# BRDCAST_FRAMES_WITH_ERROR = 0

|# FRAMES_RECEIVED_WITH_ONLY_CRCERROR = 0

|# VALID_LENGTH_FRAMES_WITH_CRC_ERROR = 0

|# JABBER_FRAMES = 0

|# FRAGMENTED_FRAMES = 0

|# INVALID_FRAMES_RECEIVED = 0

|# FRAMES_RECEIVED_GOOD = 4560013

|# PAUSE_FRAMES_RECEIVED = 0

|# UNICAST_CONTROL_FRAMES = 0

|# MULTICAST_CONTROL_FRAMES = 0

|# UNICAST_FRAMES_RECEIVED_GOOD = 4560013

|# MULTICAST_FRAMES_RECEIVED_GOOD = 0

|# BRDCAST_FRAMES_GOOD = 0

|# DATA_AND_PADDING_OCTETS_RECEIVED_GOOD= 209760598

|# COMPREHENSICE_OCTETS_RECEIVED = 291840832

|# FRAMES_WITH_SIZE_64_BYTES = 4560013

|# FRAMES_BETWEEN_SIZE_64AND127_BYTES = 0

|# FRAMES_BETWEEN_SIZE_128AND255_BYTES = 0

|# FRAMES_BETWEEN_SIZE_256AND511_BYTES = 0

|# FRAMES_BETWEEN_SIZE_512AND1K_BYTES = 0

|# FRAMES_BETWEEN_SIZE_1KND1518_BYTES = 0

|# FRAMES_BETWEEN_SIZE_ABOVE1519_BYTES = 0

===================================================================

| MAC TX STATS REGISTER CHECK

===================================================================

|# FRAMES_RECEIVED_WITH_ERROR = 0

|# UNICAST_FRAMES_WITH_ERROR = 0

|# MULTICAST_FRAMES_RECEIVED_WITH_ERROR = 0

|# BRDCAST_FRAMES_WITH_ERROR = 0

|# FRAMES_RECEIVED_WITH_ONLY_CRCERROR = 0

|# VALID_LENGTH_FRAMES_WITH_CRC_ERROR = 0

|# JABBER_FRAMES = 0

|# FRAGMENTED_FRAMES = 0

|# INVALID_FRAMES_RECEIVED = 0

|# FRAMES_RECEIVED_GOOD = 4560013

|# PAUSE_FRAMES_RECEIVED = 0

|# UNICAST_CONTROL_FRAMES = 0

|# MULTICAST_CONTROL_FRAMES = 0

|# UNICAST_FRAMES_RECEIVED_GOOD = 4560013

|# MULTICAST_FRAMES_RECEIVED_GOOD = 0

|# BRDCAST_FRAMES_GOOD = 0

|# DATA_AND_PADDING_OCTETS_RECEIVED_GOOD= 209760598

|# COMPREHENSICE_OCTETS_RECEIVED = 291840832

|# FRAMES_WITH_SIZE_64_BYTES = 4560013

|# FRAMES_BETWEEN_SIZE_64AND127_BYTES = 0

|# FRAMES_BETWEEN_SIZE_128AND255_BYTES = 0

|# FRAMES_BETWEEN_SIZE_256AND511_BYTES = 0

|# FRAMES_BETWEEN_SIZE_512AND1K_BYTES = 0

|# FRAMES_BETWEEN_SIZE_1KND1518_BYTES = 0

======================================================================

| MAC RX STATS REGISTER CHECK

======================================================================

|# FRAMES_RECEIVED_WITH_ERROR = 0

|# UNICAST_FRAMES_WITH_ERROR = 0

|# MULTICAST_FRAMES_RECEIVED_WITH_ERROR = 0

|# BRDCAST_FRAMES_WITH_ERROR = 0

|# FRAMES_RECEIVED_WITH_ONLY_CRCERROR = 0

|# VALID_LENGTH_FRAMES_WITH_CRC_ERROR = 0

|# JABBER_FRAMES = 0

|# FRAGMENTED_FRAMES = 0

|# INVALID_FRAMES_RECEIVED = 0

|# FRAMES_RECEIVED_GOOD = 9120026

|# PAUSE_FRAMES_RECEIVED = 0

|# UNICAST_CONTROL_FRAMES = 0

|# MULTICAST_CONTROL_FRAMES = 0

|# UNICAST_FRAMES_RECEIVED_GOOD = 9120026

|# MULTICAST_FRAMES_RECEIVED_GOOD = 0

|# BRDCAST_FRAMES_GOOD = 0

|# DATA_AND_PADDING_OCTETS_RECEIVED_GOOD= 456001300

|# COMPREHENSICE_OCTETS_RECEIVED = 620161768

|# FRAMES_WITH_SIZE_64_BYTES = 4560013

|# FRAMES_BETWEEN_SIZE_64AND127_BYTES = 4560013

|# FRAMES_BETWEEN_SIZE_128AND255_BYTES = 0

|# FRAMES_BETWEEN_SIZE_256AND511_BYTES = 0

|# FRAMES_BETWEEN_SIZE_512AND1K_BYTES = 0

|# FRAMES_BETWEEN_SIZE_1KND1518_BYTES = 0

|# FRAMES_BETWEEN_SIZE_ABOVE1519_BYTES = 0

% TEST_1588 0 1 10G

CONFIGURE CHANNEL 0 as master

configure_to_10G

setting up mac with a basic working config

setting 0xC5C4 into rxmac primary address Reg-1

setting 0xC3C2C1C0 into rxmac primary address Reg-0

enabling: pad and crc stripping in rx mac

testing Configure Period and Adjustment RX XGMII TSU

Configure Period and Adjustment TX XGMII TSU

clearing mac stats registers

testing Configure Period and Adjustment RX XGMII TSU

Configure Period and Adjustment TX XGMII TSU

Configure TOD Master

Configure TOD 10G

Disabling serial PMA Loopback (local)

Read back Serial PMA loopback register = 0x00000000

CONFIGURE CHANNEL 1 as slave

configure_to_10G

setting up mac with a basic working config

setting 0xC5C4 into rxmac primary address Reg-1

setting 0xC3C2C1C0 into rxmac primary address Reg-0

enabling: pad and crc stripping in rx mac

testing Configure Period and Adjustment RX XGMII TSU

Configure Period and Adjustment TX XGMII TSU

clearing mac stats registers

testing Configure Period and Adjustment RX XGMII TSU

Configure Period and Adjustment TX XGMII TSU

Configure TOD Master

Configure TOD 10G

Disabling serial PMA Loopback (local)

Read back Serial PMA loopback register = 0x00000000

Select 1588 traffic controller

Start TOD synchronization

Master 1588 start 1 step operation

TRAFFIC_CONTROLLER_BASE_ADDR: 0x100000

Waiting capturing offset delay ...

-- Break

Start capturing offset delay ...

Reset Master 1588 start 1 step operation

Reset Start TOD synchronization

delay ns = 0x00000030

delay fns = 0x00007197

offset ns = 0x00000000

offset fns = 0x00000000

===================================================================

| MAC TX STATS REGISTER CHECK

===================================================================

|# FRAMES_RECEIVED_WITH_ERROR = 0

|# UNICAST_FRAMES_WITH_ERROR = 0

|# MULTICAST_FRAMES_RECEIVED_WITH_ERROR = 0

|# BRDCAST_FRAMES_WITH_ERROR = 0

|# FRAMES_RECEIVED_WITH_ONLY_CRCERROR = 0

|# VALID_LENGTH_FRAMES_WITH_CRC_ERROR = 0

|# JABBER_FRAMES = 0

|# FRAGMENTED_FRAMES = 0

|# INVALID_FRAMES_RECEIVED = 0

|# FRAMES_RECEIVED_GOOD = 0

|# PAUSE_FRAMES_RECEIVED = 0

|# UNICAST_CONTROL_FRAMES = 0

|# MULTICAST_CONTROL_FRAMES = 0

|# UNICAST_FRAMES_RECEIVED_GOOD = 0

|# MULTICAST_FRAMES_RECEIVED_GOOD = 0

|# BRDCAST_FRAMES_GOOD = 0

|# DATA_AND_PADDING_OCTETS_RECEIVED_GOOD= 0

|# COMPREHENSICE_OCTETS_RECEIVED = 0

|# FRAMES_WITH_SIZE_64_BYTES = 0

|# FRAMES_BETWEEN_SIZE_64AND127_BYTES = 0

|# FRAMES_BETWEEN_SIZE_128AND255_BYTES = 0

|# FRAMES_BETWEEN_SIZE_256AND511_BYTES = 0

|# FRAMES_BETWEEN_SIZE_512AND1K_BYTES = 0

|# FRAMES_BETWEEN_SIZE_1KND1518_BYTES = 0

======================================================================

| MAC RX STATS REGISTER CHECK

======================================================================

|# FRAMES_RECEIVED_WITH_ERROR = 0

|# UNICAST_FRAMES_WITH_ERROR = 0

|# MULTICAST_FRAMES_RECEIVED_WITH_ERROR = 0

|# BRDCAST_FRAMES_WITH_ERROR = 0

|# FRAMES_RECEIVED_WITH_ONLY_CRCERROR = 0

|# VALID_LENGTH_FRAMES_WITH_CRC_ERROR = 0

|# JABBER_FRAMES = 0

|# FRAGMENTED_FRAMES = 0

|# INVALID_FRAMES_RECEIVED = 0

|# FRAMES_RECEIVED_GOOD = 0

|# PAUSE_FRAMES_RECEIVED = 0

|# UNICAST_CONTROL_FRAMES = 0

|# MULTICAST_CONTROL_FRAMES = 0

|# UNICAST_FRAMES_RECEIVED_GOOD = 0

|# MULTICAST_FRAMES_RECEIVED_GOOD = 0

|# BRDCAST_FRAMES_GOOD = 0

|# DATA_AND_PADDING_OCTETS_RECEIVED_GOOD= 0

|# COMPREHENSICE_OCTETS_RECEIVED = 0

|# FRAMES_WITH_SIZE_64_BYTES = 0

|# FRAMES_BETWEEN_SIZE_64AND127_BYTES = 0

|# FRAMES_BETWEEN_SIZE_128AND255_BYTES = 0

|# FRAMES_BETWEEN_SIZE_256AND511_BYTES = 0

|# FRAMES_BETWEEN_SIZE_512AND1K_BYTES = 0

|# FRAMES_BETWEEN_SIZE_1KND1518_BYTES = 0

|# FRAMES_BETWEEN_SIZE_ABOVE1519_BYTES = 0

===================================================================

| MAC TX STATS REGISTER CHECK

===================================================================

|# FRAMES_RECEIVED_WITH_ERROR = 0

|# UNICAST_FRAMES_WITH_ERROR = 0

|# MULTICAST_FRAMES_RECEIVED_WITH_ERROR = 0

|# BRDCAST_FRAMES_WITH_ERROR = 0

|# FRAMES_RECEIVED_WITH_ONLY_CRCERROR = 0

|# VALID_LENGTH_FRAMES_WITH_CRC_ERROR = 0

|# JABBER_FRAMES = 0

|# FRAGMENTED_FRAMES = 0

|# INVALID_FRAMES_RECEIVED = 0

|# FRAMES_RECEIVED_GOOD = 0

|# PAUSE_FRAMES_RECEIVED = 0

|# UNICAST_CONTROL_FRAMES = 0

|# MULTICAST_CONTROL_FRAMES = 0

|# UNICAST_FRAMES_RECEIVED_GOOD = 0

|# MULTICAST_FRAMES_RECEIVED_GOOD = 0

|# BRDCAST_FRAMES_GOOD = 0

|# DATA_AND_PADDING_OCTETS_RECEIVED_GOOD= 0

|# COMPREHENSICE_OCTETS_RECEIVED = 0

|# FRAMES_WITH_SIZE_64_BYTES = 0

|# FRAMES_BETWEEN_SIZE_64AND127_BYTES = 0

|# FRAMES_BETWEEN_SIZE_128AND255_BYTES = 0

|# FRAMES_BETWEEN_SIZE_256AND511_BYTES = 0

|# FRAMES_BETWEEN_SIZE_512AND1K_BYTES = 0

|# FRAMES_BETWEEN_SIZE_1KND1518_BYTES = 0

======================================================================

| MAC RX STATS REGISTER CHECK

======================================================================

|# FRAMES_RECEIVED_WITH_ERROR = 0

|# UNICAST_FRAMES_WITH_ERROR = 0

|# MULTICAST_FRAMES_RECEIVED_WITH_ERROR = 0

|# BRDCAST_FRAMES_WITH_ERROR = 0

|# FRAMES_RECEIVED_WITH_ONLY_CRCERROR = 0

|# VALID_LENGTH_FRAMES_WITH_CRC_ERROR = 0

|# JABBER_FRAMES = 0

|# FRAGMENTED_FRAMES = 0

|# INVALID_FRAMES_RECEIVED = 0

|# FRAMES_RECEIVED_GOOD = 0

|# PAUSE_FRAMES_RECEIVED = 0

|# UNICAST_CONTROL_FRAMES = 0

|# MULTICAST_CONTROL_FRAMES = 0

|# UNICAST_FRAMES_RECEIVED_GOOD = 0

|# MULTICAST_FRAMES_RECEIVED_GOOD = 0

|# BRDCAST_FRAMES_GOOD = 0

|# DATA_AND_PADDING_OCTETS_RECEIVED_GOOD= 0

|# COMPREHENSICE_OCTETS_RECEIVED = 0

|# FRAMES_WITH_SIZE_64_BYTES = 0

|# FRAMES_BETWEEN_SIZE_64AND127_BYTES = 0

|# FRAMES_BETWEEN_SIZE_128AND255_BYTES = 0

|# FRAMES_BETWEEN_SIZE_256AND511_BYTES = 0

|# FRAMES_BETWEEN_SIZE_512AND1K_BYTES = 0

|# FRAMES_BETWEEN_SIZE_1KND1518_BYTES = 0

|# FRAMES_BETWEEN_SIZE_ABOVE1519_BYTES = 0

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mark,

I presume you are still using below ref design "unchanged" or you had modified the design ?

Let's clarify your problem statement before we discuss about debug plan :

- Your latest update mentioned 1588 hardware testing sometime pass, sometime failed, right ?

- Does the failure occurs randomly or always after 2nd time of 1588 hardware testing ?

- Does reset the system and retest 1588 makes it to pass again ?

- When 1588 test failed, does the statistic log always show zero value ? This looks to me your design or system is stuck rather than receive wrong/bad data issue

For the debug plan, similar approach applied as I explained to you earlier on the other post

- Does your board provide clean and stable clocking to ref design mm_clk (125MHz), ref_clk_10g (644.53MHz), ref_clk_1g (125MHz) ?

- Does your board supply (100Mhz - 125MHz) clock to FPGA clkusr pin that's in charge to provide clocking to transceiver channel power up calibration ?

- The ref design comes with stp1.stp debug signal_tap file. Can you trigger and capture the signal_tap debug signals for both passing and failing condition and share with me the signal_tap files ? We can then review the signal_tap files to see which status signal is failing and debug further from there

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Deshi and team

1. I use the design is build by my workmate , he is reference to the example " Arria 10 Scalable 10G Ethernet MAC+ Native PHY with IEEE1588v2 Design “;

2.My design is running 1588V2 test success on the demo board "Arria 10 SOC Development Kit" ;

3. MY design running "TEST_SMA_LB" and " TEST_PHYSERIAL_LOOPBACK" test success on my board;

4. Every time running ”TEST_PHYSERIAL_LOOPBACK“,and then running "TEST_1588" 。1588TEST is success 。 THis the only method to made 1588TEST success now 。IF didnot running "TEST_PHYSERIAL_LOOPBACK" before "TEST_1588" , 1588 test fail, and the statistic log always show zero value;

5. Clock On my board is :

(1) clock to FPGA clkusr (100Mhz );

(2) ref_clk_10g (644.53MHz);

(3) mm_clk (100MHz);

(4) ref_clk_1g ( "no clock input " ),

There have no clock 125Mhz for the "ref_clk_1g" on my board , In my design did not need 1g test.

THANKS

Regards,

mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Deshi and team

In addition :

I set the "IOPLL" out2 is 125Mhz ,and use it as the "IOPLL2 ” ref_clk_input , IOPLL2 output the "tod sync" and "sampling clock".

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Deshi

1. When 1588 test passing I can trigger and capture the signal_tap debug signals;(The "1588_test_passing" file is in the enclosure)

2 .Whe 1588 test failing I can trigger and capture anything , as the ip core never running .

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Deshi and team

I have modify my board clock by program the chip Si5338A, and now my board clock is :

(1) clock to FPGA clkusr (100Mhz );

(2) ref_clk_10g (644.53MHz);

(3) mm_clk (125MHz);

(4) ref_clk_1g ( 125MHz );

but the 1588 test is never improve

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Deshi and team

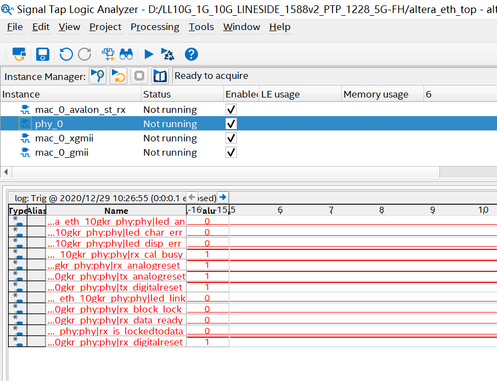

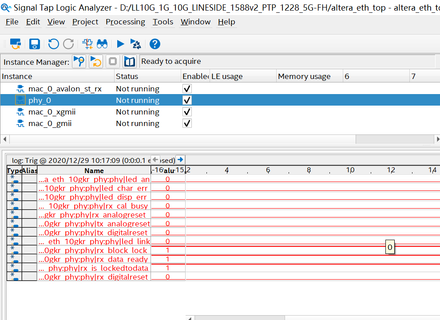

1. I had run the 1588 test project on my board with Optical fiber between 0 port and 1 port , when I run Signal Tap to get 0 port phy interface signal , I get an abnormal signal , the phy is being calibrated:

Under these circumstances,running 1588_TEST , Fail

2. Every time after running ”TEST_PHYSERIAL_LOOPBACK 1 10G 5000“ , The Signal Tap get an normal signal about 0 port phy interface :

Under these circumstances,running 1588_TEST , succes

- Tags:

- e

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mark,

Pls use the original working ref design without design modification. Just change the FPGA OPN and pin location to match your board only.

- Once getting the design to work then only feel free to modify the design

Let's debug your following statement first

- When 1588 test failing I can't trigger and capture anything , as the ip core never running

Can you share with me the signal_tap screenshot/file when the 1588 test is failing ?

- I want to know what's the exact signal condition that you see from signal_tap in test failed condition.

Let me explain. Which scenario that you are facing here ?

- Scenario A :

- Signal_tap is clocked by "xgmii_clk_312_5". Once the xgmii clock presented on your board, signal_tap should start capture something (be it good or bad signal status) if you set the signal_tap trigger condition to capture everything xx. Don't set trigger condition like trigger on rising edge or faling edge

- The only reason signal_tap will stop working is there is no clock on xgmii_clk_312_5. Signal_tap will complain "waiting for clock". Are you seeing scenario A ?

- No clock could be due to your board stop supplying input clock to FPGA or FPGA IOPLL loose lock or your design is stuck in reset. Then you can check further from here

- Scenarion B :

- Signal_tap detected "xgmii_clk_312_5" and start capturing data.

- But you set signal_tap trigger condition on some signal and the signal didn't trigger causing nothing capture on your signal_tap because it's still waiting for signal trigger.

- Pls set the signal_tap trigger condition to capture everything xx. Don't set trigger condition like trigger on rising edge or faling edge

- Then we see what's signal status result on the signal_tap

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Deshi

the STP is in the appendix,pls check up

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

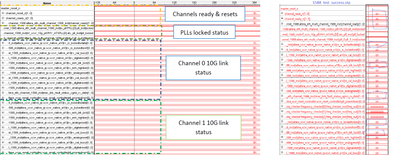

SIgnal_Tap result comparison between ref design doc (page 14) vs customer 1588_test_passed result

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI Mark,

May I know

- stp_1588_TEST_success.stp = 1588 test passed result ?

- stp_1588_TEST_fail.stp = 1588 test failed result ?

The reason I asked is due to I am seeing weird result when compared to golden reference signal_tap result from ref design doc (page 14). Attached is the result comparison that you can check it out yourself.

I suspect is either

- (A) Something is still wrong with your board or system reset control on 1588 ref design "channel_reset_n" and "master_reset_n" ports

- Or (B) your signal_tap result is capturing the system test run at the wrong time (like before the system is stable or after test run completed)

We now know that signal_tap is working on your board. You can then play with signal_tap trigger feature to try detect following expected signal behaviour

- For instance, your signal_tap result shown transceiver channel is still stuck in reset and ready signal haven't asserted high

- both ch0 and ch1 rx_islockedtodata signal doesn't assert high which means Rx channel CDR doesn't detect correct 10G data and lock yet

- both ch0 and ch1 rx_enh_blk_lock signal doesn't assert high as well which highly due to CDR is still loose lock ?

- ch0 link_fault status signal also asserted high which is bad

Pls try play around with trigger function and re-capture signal_tap result for both passing and failing cases then we can compared the result again.

- You can do so yourself to compare with page 14 expected signal_tap result in parallel

- Then we can exchange debug opinion to discuss further

Thanks.

Regards,

Deshi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Deshi

- stp_1588_TEST_success.stp = 1588 test passed result ? YES

- stp_1588_TEST_fail.stp = 1588 test failed result ? YES

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Deshi and team

I have try to make 1588V2 channel 0 loopback to channel1 on the chip without Optical module。My code is:

" assign rx_serial_data[0] = tx_serial_data[1] ;

assign rx_serial_data[1] = tx_serial_data[0] ;”

then compilation, I get error about this :

Error(11654): Output port "VOP" of "HSSI_PMA_TX_BUF" cannot connect to HSSI port "RX_P_BIDIR_IN" of "HSSI_PMA_TX_BUF" for atom "altera_eth_multi_channel_1588_inst|CHANNEL[1].altera_eth_channel_1588_inst|phy|xcvr_10gkr_a10_0|CHANNEL|DATAPATH_10G.NATIVE_PHY_10G_1588_644_LS.native_10g_1588_644_ls_inst|native_10g_1588_644_ls_inst|native_10g_1588_644_ls_inst|g_xcvr_native_insts[0].twentynm_xcvr_native_inst|twentynm_xcvr_native_inst|inst_twentynm_pma|gen_twentynm_hssi_pma_tx_buf.inst_twentynm_hssi_pma_tx_buf".

Error(11654): Output port "VOP" of "HSSI_PMA_TX_BUF" cannot connect to HSSI port "RXP" of "HSSI_PMA_RX_BUF" for atom "altera_eth_multi_channel_1588_inst|CHANNEL[1].altera_eth_channel_1588_inst|phy|xcvr_10gkr_a10_0|CHANNEL|DATAPATH_10G.NATIVE_PHY_10G_1588_644_LS.native_10g_1588_644_ls_inst|native_10g_1588_644_ls_inst|native_10g_1588_644_ls_inst|g_xcvr_native_insts[0].twentynm_xcvr_native_inst|twentynm_xcvr_native_inst|inst_twentynm_pma|gen_twentynm_hssi_pma_rx_buf.inst_twentynm_hssi_pma_rx_buf".

Error(11654): Output port "VOP" of "HSSI_PMA_TX_BUF" cannot connect to HSSI port "RXP" of "HSSI_PMA_CDR_PLL" for atom "altera_eth_multi_channel_1588_inst|CHANNEL[1].altera_eth_channel_1588_inst|phy|xcvr_10gkr_a10_0|CHANNEL|DATAPATH_10G.NATIVE_PHY_10G_1588_644_LS.native_10g_1588_644_ls_inst|native_10g_1588_644_ls_inst|native_10g_1588_644_ls_inst|g_xcvr_native_insts[0].twentynm_xcvr_native_inst|twentynm_xcvr_native_inst|inst_twentynm_pma|gen_twentynm_hssi_pma_channel_pll.inst_twentynm_hssi_pma_channel_pll".

Error(11654): Output port "VOP" of "HSSI_PMA_TX_BUF" cannot connect to HSSI port "RXP" of "HSSI_PMA_CDR_PLL" for atom "altera_eth_multi_channel_1588_inst|CHANNEL[0].altera_eth_channel_1588_inst|phy|xcvr_10gkr_a10_0|CHANNEL|DATAPATH_10G.NATIVE_PHY_10G_1588_644_LS.native_10g_1588_644_ls_inst|native_10g_1588_644_ls_inst|native_10g_1588_644_ls_inst|g_xcvr_native_insts[0].twentynm_xcvr_native_inst|twentynm_xcvr_native_inst|inst_twentynm_pma|gen_twentynm_hssi_pma_channel_pll.inst_twentynm_hssi_pma_channel_pll".

Error(11654)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

- We don't support FPGA internal loopback from one transceiver channel to another transceiver channel. That's why you get design compilation error.

- We only support FPGA internal loopback within the same transceiver channel from Tx channel back to Rx channel

Just would like to follow up with you - did you have a chance to play around with different signal_tap triggering setup to observe different signal_tap result between passing and failing case ?

- Any latest debug update to share with me ?

Thanks.

Regards,

dlim

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page