- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am implementing an OpenRISC processor on a DE0-CV board which features a Cyclone-V FPGA. I am using Quartus Prime v19.1 Standard Edition.

In my design I instantiate an Altera PLL in order to generate 2 clocks, one for the processor and one for the SDRAM controller and the on-board SDRAM. The Processor clock I want it to be 120 MHz, while the clock for the controller and the SDRAM I want it to be 100 MHz.

I see that after Compilation, I have many Reg-to-Reg Setup violations (negative slack) and at the Timing Analyzer, the "report_clock_fmax_summary" reports the following maximum frequencies for those 2 clocks:

clk_120 --> 77.14 MHz

clk_100 --> 91.14 MHz

Does anyone know how accurate are those Maximum frequencies? Is this the Maximum that the design at its current state can reach without changing it on this specific FPGA? Is there anything that can be done to push for higher frequencies without changing the design?

Any answers or sources for reading will be welcome.

Looking forward for your response.

Kind regards,

anm

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes. It is the frequency that the design can reach at this compilation. You may see a different value if you perform a seed sweep or change the compiler settings.

The value stated in Fmax summary reports potential fmax for every clock in the design, regardless of the user-specified clock periods. The "Note" column reports which analyses restricted fmax.

Thanks.

Best regards,

KhaiY

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes. It is the frequency that the design can reach at this compilation. You may see a different value if you perform a seed sweep or change the compiler settings.

The value stated in Fmax summary reports potential fmax for every clock in the design, regardless of the user-specified clock periods. The "Note" column reports which analyses restricted fmax.

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KhaiY,

thank you for your response. Can you please how to perform a seed sweep? I guess this is an initial seed for the PnR that Quartus performs, right?

Thank you in advance for your response.

Kind regards,

Nassos

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Nassos,

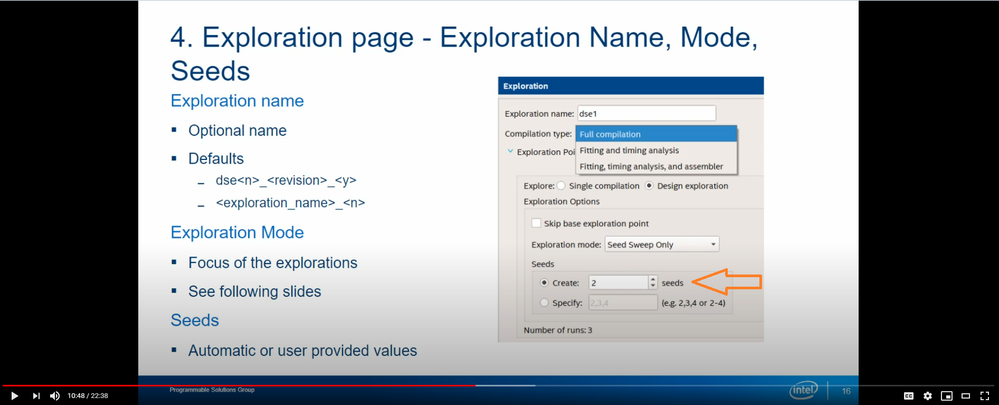

This video shows how to perform seed sweep using Design Space Explorer step by step.https://www.youtube.com/watch?v=1cc74E3zaeI

You may specify how many seeds you want to run in the setting.

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your response KhaiY and the video. They are much appreciated!

Kind regards,

Nassos

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Nassos,

No problem. I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

Best regards,

KhaiY

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page