- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi expert,

I am using Stratix 10 SoC board. And my FPGA logic needs to access flash.

In my setup, HPS boot from SD card not QSPI Flash. And QSPI locate at 0xff8d2000 in HPS's map.

I connect my bus to HPS's f2h interface and try to write data to address 0xff8d2000, but the data cannot be written into QSPI.

Is my operation correct? Does QSPI need additional setting up in this scenario?

Can you please help with that? Much thanks!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jiayi_H_Intel,

When u-boot boot up, in u-boot type help. Check for a command which is bridge. Then select bridge enable and see any difference.

Thanks.

Regards,

Aik Eu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Aik Eu,

I tied your suggestions, seems no difference. Can you please help?

Here are details of my design and test step:

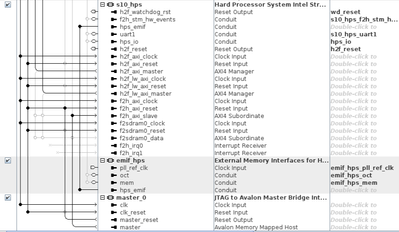

I use jtag master to access hps's f2h interface:

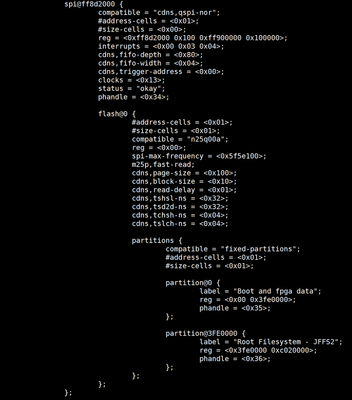

Arm device tree is:

In arm uboot boot up terminal, I type "bridge enable", and then "boot" for default boot.

In system console:

set service_paths [get_service_paths master]

set master_service_path [lindex $service_paths 1]

set claim_path [claim_service master $master_service_path mylib]

master_write_32 $claim_path 0xff8d2000 0x1234

master_read_32 $claim_path 0xff8d2000 0x1

Read returns 0x0. So my write to flash is not successfully.

Can you please help with that?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jiayi_H_Intel,

Can provide the base address of the IP involves in your qsys design?

Thanks.

Regards,

Aik Eu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jiayi_H_Intel,

Is is possible that you can sent me your design in email?

I not sure how big is the size.

Thanks.

Regards,

Aik Eu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jiayi_H_Intel,

For Stratix10, I think you may not able to access the sdm_QSPI on the FPGA side since you are booting up from sd-card. I afraid the access to the sdm_QSPI will not be allowed. Some of the boot up configuration was written in the sdm_QSPI when booting up, so simply writing to the sdm_QSPI may overwrite the configuration data.

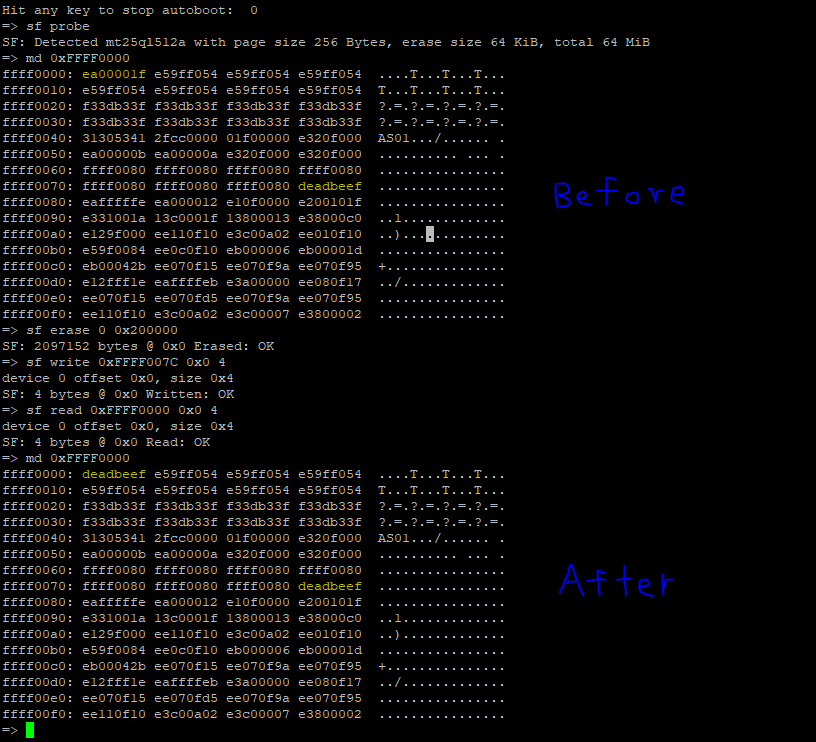

Anyway, Can try "sf probe" in U-boot and see. Do let me know what will show after that?

I think you were trying to write to to sdm_QSPI_register(0xFF8D2000), maybe can try to write to the sdm_QSPI_data_Address(0xFF900000 to 0xFF9FFFFF) instead.

Can check with the Stratix10 HPS Address Map, link as below:

https://www.intel.com/content/www/us/en/programmable/hps/stratix-10/hps.html#dap1505405910812.html

After sf probe, try the below read/write example link below using sf command in U-boot:

https://blog.krybot.com/a?ID=01550-3cc5b429-9aaf-45e5-b934-b73d31966d36

Thanks.

Regards,

Aik Eu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Aik Eu,

After "sf probe", it shows:

SF: Detected mt25qu02g with page size 256 Bytes, erase size 4 KiB, total 256 MiB

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jiayi_H_Intel,

Is the sf write/read working? Can verify try that also and let me know.

Do perform sf probe first before sf write/read.

Thanks.

Regards,

Aik Eu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jiayi_H_Intel,

Regarding the sf cmd in order to write to QSPI flash, need to take note that you will required to perform a sf erase first before you can write into it.

example:

sf erase 0 0x200000

// Erase 2MB from QSPI offset 0x0

// Note: If erase size is less than QSPI Flash page size, u-boot reports erase error

Before running any sf cmd, you will need to execute sf probe first.

As for sf write/read cmd:

sf write will be writting the content of the memory location specified in the cmd into QSPI flash.

sf read will be reading the data from QSPI flash into the memory location specified in the cmd.

You can use U-boot md cmd to check the changes in the memory location that you specified when performing sf write/read cmd.

U-Boot read command can be used to see what is programmed in to QSPI memory.

Thanks.

Regards,

Aik Eu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Aik Eu,

Thanks for your reply. So in conclusion, the only way to access qspi flash is through sf cmd in boot stage. The function of sf cmd is to move data between flash and memory. And it is not allowed to access flash from FPGA side by F2H port. Is that correct?

And much thanks for your help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jiayi_H_Intel,

The sdm QSPI is on the FPGA side. The sf cmd we tried is one of the method to read/write from HPS side. Another method will be considering the Mailbox Client IP in your design in order to do that.

Refer to the document below for Mailbox Client IP:

Normally is not advisable to write on the sdm QSPI as some of the FPGA configuration data is written there while booting up from sd card for the case of Stratix 10 devices.

Anyway if you are confident that you will not overwrite those data, then probably can consider doing so for your system operation.

Thanks.

Regards,

Aik Eu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jiayi_H_Intel,

I will close this thread if no further question. Do consider open a new thread if there is new follow up question.

Thanks.

Regards,

Aik Eu

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page