- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am currently using hard memory controller IP in cyclone 10 device using quartus 18.1. I have tried to simulate the example design by using default settings. I have selected the mode of calibration as skip calibration.

Memory side reset as well as user side reset is not asserting after a huge time.

Is there anything we can change in the design files so that we can run the simulation at faster speed ?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Which C10 variant are you using and are you using the Quartus Pro edition? Did you enable the abstract PHY option along with skip calibration? Those are the two main options for speeding up a simulation.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi AShah38,

Also other culprit here could be due to the simulation tools that using by user.

You may refer to the information from user guide --> https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-20116.pdf

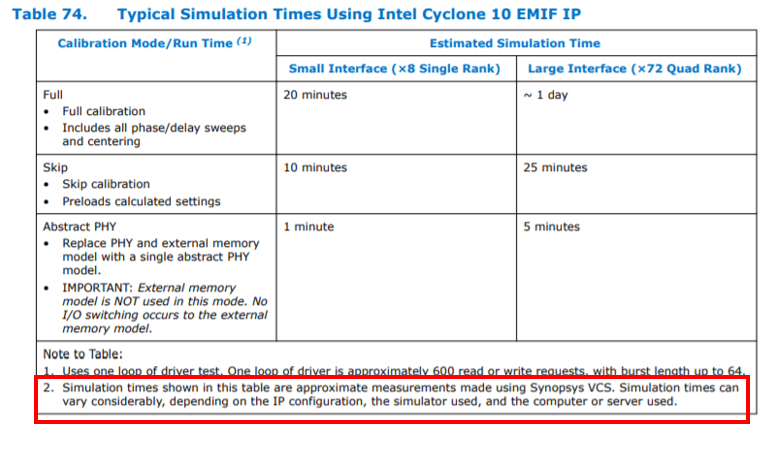

Table 74. Typical Simulation Times Using Intel Cyclone 10 EMIF IP (page 89) stated that:

- Simulation times shown in this table are approximate measurements made using Synopsys VCS. Simulation times can vary considerably, depending on the IP configuration, the simulator used, and the computer or server used.

The time indicated in this table is based on the fastest simulation tools which is VCS. And other simulation tools is expected will run with longer time. I would recommend you to try using other simulation tool. (For eg : synopsys VCS simulation run time is much faster as compared to mentor modelsim)

Hope this helps.

Thanks

Regards,

NAli1

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page