- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

i know high level async reset can be achieved like:

always@(posedge clk or posedge rst)

begin

if (rst==1)

but how to realize posedge async reset, which means the moment reset edge coming up, the logic in always block reset immediately?

i wrote the logic below:

always@(posedge clk or posedge rst)

begin

rst_pre<=rst;

if(!rst_pre && rst) // to test if rst is posedge

//execute reset logic here...

but the question is, the always block was triggered in a unexpected high frequency, i finally figured out that although there was only 1 posedge of rst, the always block was triggered by rst signal much more than 1 time. (tested using altera cyclone 10LP with quartus 18)

I think the method i used to achieve posedge async reset is not stable, can anyone tell me what can i do to solve this?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Robert,

You have to deassert the reset signal, LOW signal in your case. Otherwise, the logic cannot come out from reset state.

Thanks.

Best regards,

KhaiY

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It's not clear what you're trying to achieve here. Your first example is the way to do this. rst_pre in your second example is never going to be low because you have posedge rst in your sensitivity list (rst is high) and then assigning that to rst_pre.

Perhaps you are saying that your rst signal is truly asynchronous (pushbutton not debounced?), meaning that it could be glitching and causing issues. If this is the case, you should register it, synchronizing it to a clock domain before using it in the sensitivity list here.

If you have a Signal Tap waveform that shows the issue you're talking about, you could post it.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

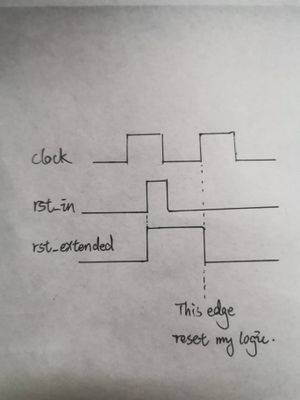

thank you, your suggestion( which indeed help) like the waveform below. i extended 'rst_in' to clock edge to register it.

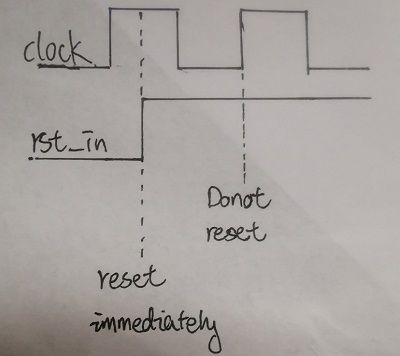

But what i want is to 'reset my logic immediately after posedge of rst_in', and do not reset when the next clock edge arrives.

if i use the logic below, the logic will be reset more than one time, if the high level rst_in last for a long time.

always @ (posedge clk or posedge rst_in )

begin if (rst_in) ...

you said the second logic i mentioned can't achieve that, but i think: the moment the posedge rst_in arrives, 'rst_pre' will not change immediately because i use '<=' rather than '='. so it will still keep the value of 0, while 'rst_in' is 1.

thank you for your help! maybe my question is weird (i just too eager to know the answer...)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The logic will not come out from reset state if you do not deassert the reset signal.

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thank you!

but, what i want to achieve is to posedge reset rather than high level reset.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Robert,

You have to deassert the reset signal, LOW signal in your case. Otherwise, the logic cannot come out from reset state.

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

Best regards,

KhaiY

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page