- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I am integrating the I2C slave to Avalon MM Master bridge IP inside my project for Cyclone 10 LP but it is still unclear how this IP works.

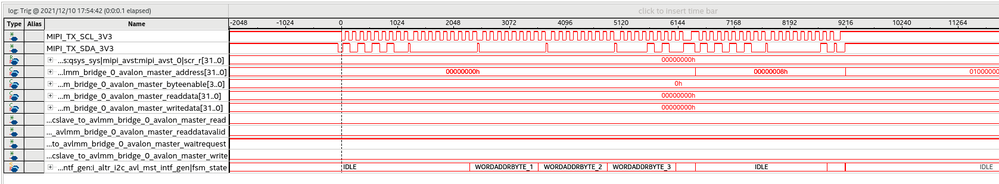

Here you can find the SignalTap attached to both I2C lanes and Avalon MM Master signals. From the host side I am sending the device address (0x55 selected in the qsys parameter of the IP), 4 byte address (0x0000000A) and one byte of data (0x01). Also considering 4 byte of data (0x00000001) the behavior is the same.

As you can see, the IP correctly acknowledges the master communication but the Avalon MM address and data are not correctly set, as well as the write signal.

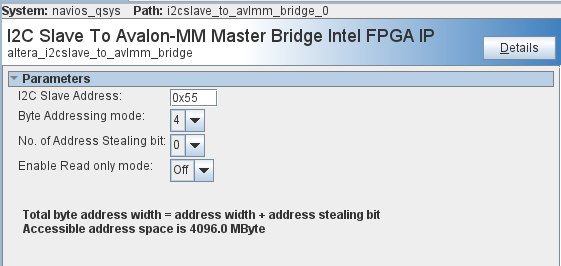

In the following image, you can see the qsys settings for the I2C slave to Avalon MM Master bridge IP:

Which is the correct data that I have to send via I2C? I have to write the following data into the Avalon MM via I2C:

Avalon MM address: 0x0000000A

Avalon MM data to write: 0x00000001

Thank you.

コピーされたリンク

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I'm not an I2C expert, but shouldn't the address you want to put on the Avalon bus (0xA) be in the second byte from I2C, not 4 bytes later? I'm presuming the first byte is the control byte. Are you following the Embedded Peripherals IP user guide (page 202 of the pdf)?:

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_embedded_ip.pdf

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi there I have been reading that page on the guide but still confused on how the final packet of data will look like. I am trying to send the packet from the system console and confused on how to define the address.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi fedecive,

Any update on this thread?

Best regards,

Sheng

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Sheng,

yes, I was able to resolve the issue. We can close the thread.

Thank you.